- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用24位Δ-Σ ADC高精度测量模拟小信号

尽管增加积分器级数和增大过采样率可以进一步降低噪声,但是稳定性是3阶或更高阶Δ-Σ转换器需要关注的大问题。一旦Δ-Σ调制器出现不稳定,那么除非重新开关电源,否则它们通常不会再次变至稳定状态。凌特公司的所有Δ-Σ转换器都采用3阶调制器,而且每次转换都对调制器和滤波器复位。即使调制器进入不稳定状态(这很可能发生在基准电压很低,输入信号又很大的情况下),其Δ-Σ ADC也可以在不需要开关电源的情况下自己恢复到稳定状态。

|

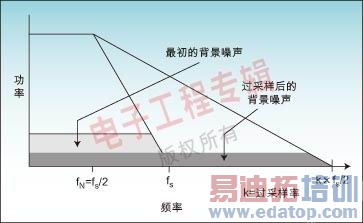

图2:过采样降低了所关注频带中的背景噪声。 |

调制器环路稳定且噪声由积分器修整后,接下来对所产生的数字信号进行滤波和抽取。抽取就是舍弃一些采样,主要是去掉由过采样带来的冗余信号信息。如果过采样率为256,那么ADC求取256个采样的平均值,而抽取器则每256个采样产生1个数字输出。滤波和抽取后产生的数字信号再从ADC输出,一般采取串行格式。

Δ-Σ ADC的数字输出与基准源一样好,有噪声的基准源是任何数据转换器的主要误差来源。Δ-Σ调制器的1位DAC由正基准电压和负基准电压偏置。正(或高)基准电压一般是输入信号电平的上限,而负(或低)基准电压一般是下限。有些Δ-Σ ADC的正和负基准电压都连接到外部,某些则将低的基准连接到公共电压上,例如地,其它ADC可以选择使用内部带隙基准(bandgap reference)或外部基准。凌特公司的Δ-Σ转换器允许设计师改变基准和输入共模电压,变化范围在地到电源电压之间。

在选择Δ-Σ转换器时,转换时钟和数据延迟是两个需要考虑的重要因素。时钟控制数据处理的内部时序,并决定转换时间。转换时钟可以从内部提供,或者采用外部晶振或硅振荡器。不过,因为数字滤波器不抑制振荡器频率,因此采用内部振荡器具有优势。

|

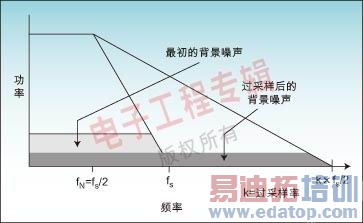

图3:积分器将噪声强制推移到更高的频率上。 |

由于数据延迟,当前输出结果落后于输入一个采样周期。凌特公司所有无延迟Δ-Σ转换器都在一个周期内稳定,简化了多路复用应用。

Δ-Σ ADC虽然本质上很简单,但是配置这种ADC却常常是一个复杂的过程,如要写很多指令、平衡输入级的复杂性和选择外部振荡器。凌特公司的Δ-Σ转换器没有校准序列、配置寄存器、滤波器稳定时间和外部振荡器,降低了设计的复杂性。每个转换周期中都执行透明的偏移和满标度自动校准,以确保高准确度,而高准确度则保证能够分辨出1克或0.01度的差别。

作者:Steve Logan

产品行销工程师

凌特公司

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:解析两项值得期待的短距离技术:RF遥控器和无线充电

下一篇:解决手机中的WiMax、蓝牙和Wi-Fi共存问题的设计挑战