- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

芯片上下RF系统集成化多层薄膜技术

摘要 本文主要论述了有集成化无源器件的多层薄膜晶圆片级封装技术,该技术有助于使高频率应用的高Q器件集成化。

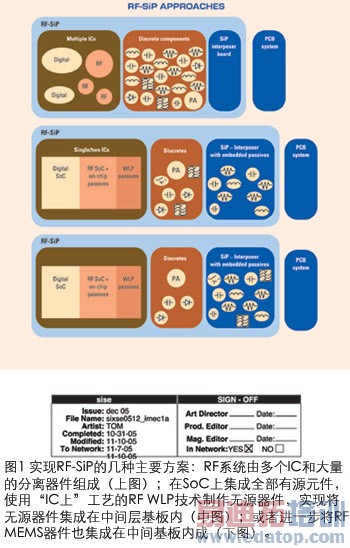

随着无线通信器件在数量和品种方面变得越来越丰富,高密度系统集成化,正成为一种极其重要的发展要求。RF无线电器件的高密度集成化不但要求有源器件(RF片上系统,RF-SoC)的集成化,而且也要求大量无源器件和功能块的集成化。所以,要求RF系统合适的划分技术。有源器件也可集成于一个或两个SoC器件上,并且应把外部无源器件集成于SoC封装中,有效地实现系统级封装RF(RF-SiP,如图1所示)。

实现具有集成化无源器件的RF-SiP“插件”基板的关键性技术,就是多层薄膜技术,即用于晶圆片级封装技术(WLP)——器件晶圆片的(再分布和形成凸点技术)。此技术的主要特点是,使用对各种无源电路元件确定的光刻技术,形成高度微型化和高图案成形精度,具有微米和亚微米等级容差范围。

多层薄膜技术

多层薄膜技术主要的特点,是使用像晶圆片一样的工艺步骤和光刻法。开发此技术的基础是WLP或硅后端线(BEOL)工艺技术。有自动化装卸的高容积制造设备,适用于普通硅晶圆片尺寸。

此技术的基本要素是薄膜、高密度金属化技术和薄膜电介质淀积技术,为了考虑结构中不同层之间的高密度互连,能够实现隔离层中很小的通孔。

薄膜技术,非常适合于无源元件的集成化和微型化。为了形成优质电阻器或电容器层,可用高重复性淀积复杂的各种材料。薄膜光刻法可确保高尺寸精度,能够实现小的容差并增加微型化,所以,避免了对电阻器或电容器数值的“微调”。电镀铜线,如上所述,完全适合于实现高质量电感器,特别是要求高频率应用的领域。

RF-SiP

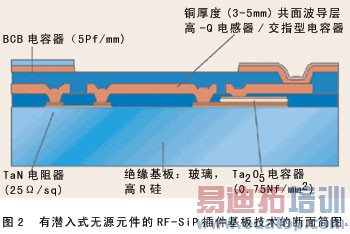

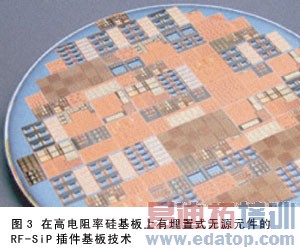

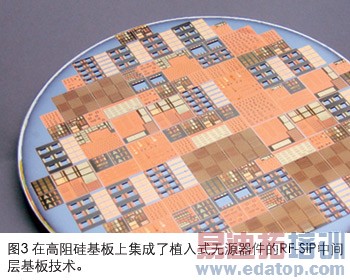

由上所述,薄膜WLP技术可用于实现有集成化无源元件的互连基板技术。图2和图3示出了在IMEC公司研发的RF-SiP构造技术示例。

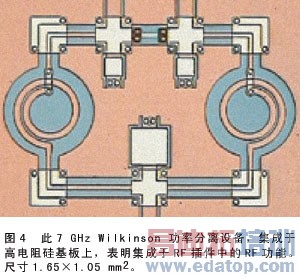

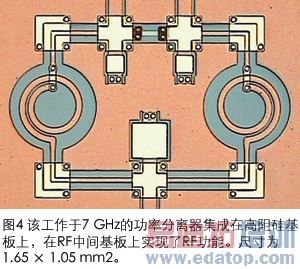

在低损耗RF基板上(玻璃或高电阻率硅),把集成化电阻器、电容器和电感器进行集成。为了考虑此技术的实际应用,开发了设计程序库。该程序库不仅由所有相关RF无源电路的电学上的等效电路模型,而且由互连线模型、不连续性和引线键合或倒装片连接组成。这些模型具有主要的几何尺寸参量,要考虑RF设计的柔性最佳化。该程序库也在自动化方面形成了电路掩模布局,从而更进一步地改进了设计电路的可预测性。采用此方法,可有效地实现复杂滤波器、耦合结构和滤波器功能。应用示例如图4所示。

“IC正上方”RF-SoC

RF前端ICs的特点,就是片上电感器占有相对大的面积。这些电感器的大尺寸,是由比例电感器的物理限制范围造成的,从而保持其性能(Q因素)。在RF-SiP插件基板上,实现这些电感器,如上所述,由于互连寄生现象,通常不是随意的,甚至对小的倒装芯片凸点而言,这会降低采用高-Q片下电感器获得的性能优化能力。然而,集成化无源技术,也可直接应用于器件晶圆片上或“IC正上方”。

通过把螺旋电感器置于薄膜层中——“IC正上方”——极大地增加了螺旋电感器和损耗基板之间的距离。通过采用较厚、电镀的铜电感器,获得较低的耐电痕性。

这种电感器工艺的聚焦离子束断面图,如图5所示。在此状况,使用10mm厚度的铜层和12mm厚度的介质。在10mΩ-cm硅CMOS晶圆片上,得到具有Q因素超过30多达5GHz的电感器。甚至通过在硅基板上,应用接地屏蔽可增大Q因素。再者,可实现具有高质量因素的差分电感器和非常高的共振频率,如图6所示。

结语

具有集成化无源元件的多层薄膜WLP技术既可应用于有源晶圆片(RF-SoC),也可应用于中间玻璃层上或高电阻率硅基板上(RF-SiP)。结果证明,薄膜技术在集成化高Q 无源元件应用于无线通讯方面,已做好准备工作。其频率范围非常宽广,从1-5GHz手机标准到多达77 GHz的汽车雷达。

参考原文:用于片上和片外RF系统集成的多层薄膜技术(本文作者:Eric Beyne Walter De Raedt Geert Carchon IMEC )

随着无线通信器件数 量和种类的不断增 长,对高密度系统 集成的需求变的越 来越强烈。高密度集成不仅要求RF器件内包含有源元件(RF系统级芯片[RF-SoC]),还要求在系统内集成数目众多的无源元件,例如传输线、电阻元件、电容元件和电感元件,以及像滤波器及变压器之类的功能模块。为了减小集成系统的物理尺寸并从降低成本的角度考虑,还需要实现更高的集成度。但这些元件无法像有源IC技术那样,可以进行等比例缩小,因此将所有无源元件都实现片上集成的难度很大。为了克服这一难题,首先需要对RF系统进行合理划分。将所有的有源器件集成到一个或者两个SoC芯片上,其他的无源器件则可以在SoC封装中完成,这样可以有效地实现RF系统级封装(RF-SiP,图1)。

这种用于RF-SiP的“中间层”基板可以用于集成有无源元件。而实现这种基板的关键就在于器件晶圆的制作过程(再分布和凸点成型)采用了多层薄膜技术—该技术也可同样应用于晶圆级封装(WLP)。这种技术最为突出的特点是采用光刻显影工艺来制作各种无源电路元件。采用这项工艺可以获得很高的集成度和图形精度,图形尺寸的容差范围可达微米和亚微米量级。这就保证了电路制作具有很高的可重复性和可预测性—这些性能对于实现器件的一次成功和高生产产率至关重要。

随着晶体管尺寸的持续等比例缩小,以及在微波和毫米波通讯领域CMOS和SiGe器件取代GaAs器件的速度不断提高,高频电路的性能越来越依赖于其片上无源器件的性能。然而,为了跟随这种尺寸缩小的变革需要更薄的片上金属层和介电层,这种变化却会降低片上无源元件的Q值。一种成本合适且颇具吸引力的解决方案是通过薄膜WLP技术实现片上电感,这种方法同以往在RF-SiP中间层基板上集成无源元件的方法类似。

多层薄膜技术

多层薄膜技术最突出的特点是采用了类似晶圆加工的工艺方法和光刻技术。开发多层薄膜技术的出发点是用于WLP和硅加工中的后道工艺(BEOL)。目前可以自动适应各种尺寸的普通硅晶圆,并可用于大批量生产的工艺设备已经面市。

多层薄膜技术由如下几项基本技术构成:制作高密度的薄膜金属层;沉积薄膜介电层;在隔离层中实现非常小尺寸通孔,在整个结构的不同金属层之间将通过这些通孔实现互连。

薄膜技术非常适于用来集成和缩小无源元件。该技术可以以很高的可重复性沉积那些用于制造电阻和电容元件的复杂材料。薄膜光刻技术则保证了图形的尺寸精度很高,使得小图形容差和进一步缩小元件尺寸成为可能,这样也避免了“校准”电阻值或电容值的操作。通过电镀获得的铜导线层正是制作高品质因素电感元件的理想选择,特别是满足了高频应用的需要。

RF-SiP

上文所述的薄膜WLP技术可以用来制作集成了无源元件的高级互连基板。IMEC已经开发了这种RF-SiP层积技术,这方面的例子可见图2和 图3。

电阻、电容和电感元件可以被集成到低损耗的RF基板(玻璃或高阻硅)上。为了使这项技术可以方便运用,还开发了相应的支持设计库。该设计库由各种RF无源元件的等效电路模型组成,除此之外还包括多种互连线、非匹配连接和引线键和或倒装芯片的等效电路模型。这些模型同时也具有各元件的主要几何尺寸,允许对RF设计进行灵活优化。该设计库还具有自动生成电路版图的功能,进一步提高了所设计电路的可预测性。使用这种方法已经实现了复杂的滤波器、耦合结构和滤波功能。使用这种方法的一个例子如图4所示。

“IC上” RF-SoC

射频前端IC的一个重要特征是其片上电感要占用很大的芯片面积。这些电容面积庞大,是因为为了保证其品质因素(Q值),不得不受到对元件物理尺寸的限制。也可以像上面介绍的,在RF-SiP中间层基板上制作这类电感,但通常由于互连寄生效应的影响而很少被采用。即便采用尺寸很小的倒装芯片凸点作为互连,系统的高频传输性能仍将受到损害,这种损害极大地减弱了采用片外高Q值电感对系统性能带来的提高。然而,仍可直接在器件芯片上采用集成无源元件技术,或称之为“IC上”工艺。

对于很多高频RF IC来说,其性能提高的制约因素就是常规片上电感的品质因素太低。这是由于片上金属层的薄膜电阻相对较高以及半导体硅基板的损耗较高。将螺旋状电感制作在薄膜层——即采用“IC上”工艺——可以极大增加电感螺旋与高损耗基板之间的距离。除此之外通过电镀可实现较厚的铜导线层,这样也可获得低得多的布线电阻。

图5所示的是采用这种工艺制作的电感,图中为其横截面的聚焦式粒子束显微镜照片。该电感采用了10 mm厚的铜层和12 mm厚的介电层。使用电阻率为10 mm-cm的硅CMOS晶圆,在频率为5 GHz时其Q值高达30。如果在硅基板上再添加地屏蔽层,则可进一步提高电感的Q值。同样,还可以用该项技术实现高品质因素和极高谐振频率的差分电感,如图6所示。

该项技术所使用的后处理工艺与后道工艺中的铜和铝都是完全兼容的。另外该项技术的成本也较低,并且不需要增加额外的芯片面积。在完成后处理工艺之后,对MOS晶体管和后道互连进行测试,并没有发现明显的性能偏差。同利用后道工艺制作的电感相比,采用WLP工艺的电感可以得到更好的性能和更高的谐振频率,可以实现如VCO之类高性能、低功耗的电路设计。

IMEC已将该技术用于5 GHz和15 GHz低功耗VCO的设计,该设计基于90 nm CMOS工艺。5 GHz和15 GHz的VCO分别采用3 nH和0.6 nH的WLP电感,在没有地屏蔽层的情况下得到电感的差分Q值分别为40和55。另外5 GHz和15 GHz VCO的核心功耗分别低至0.33 mW和2.76 mW,相位噪声分别为-115和-105 dBc/Hz(1MHz偏置下),频率可调范围分别为148 MHz和469 MHz。为了进行比较,还在90 nm CMOS工艺条件下,采用后道工艺制作了6.3 GHz VCO,并且加入了图形化的地屏蔽层,其核心功耗5.9 mW,1 MHz时相位噪声为-118 dBc/Hz。

结论

用于集成无源器件的多层薄膜WLP技术可用于制造有源晶圆(RF-SoC),也可用于玻璃或高阻硅中间层基板(RF-SiP)。当今无线通讯元件种类繁多,要求的使用频率范围也非常宽,从移动电话标准所采用的1-5 GHz,到汽车用探测雷达所采用的77 GHz跨越很大,研究结果表明通过薄膜技术制作的高Q值无源元件可以满足无线通讯技术的要求。

13.56MHz NFC天线,13.56MHz RFID天线设计培训课程套装,让天线设计不再难

上一篇:电子收费系统综述

下一篇:EPC Gen 2软硬件工具综述