- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CST场路联合仿真实例:芯片封装辐射仿真方法

录入:edatop.com 点击:

大家好,本期将介绍CST在EDA领域里的应用案例—芯片封装辐射仿真方法。这里我们辐射信号源模型用到了IBIS模型,并模拟在该源模型下芯片封装对外辐射。

首先我们先完成芯片封装的S参数提取,这里我们接着上一篇仿真实例002:芯片封装S参数提取方法继续。我们在该案例中已经设置好了需要仿真的一对差分对。后面我们在DS(设计工作室中)对这对信号激励IBIS源模型,并观察芯片在工作下的对外辐射情况。

场仿真设置

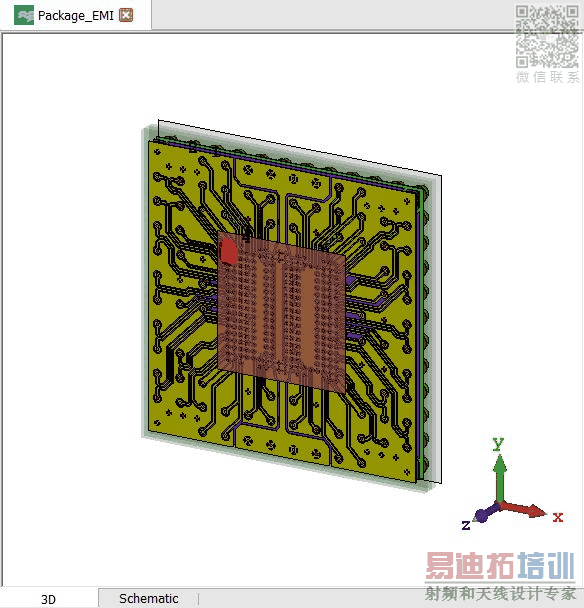

在上一篇中我们提到了使用CST的模板并如何快速EDA import得到仿真结果。这篇将之前已经完成端口导入建模的芯片封装的文件另存为Package_EMI,如下图所示:

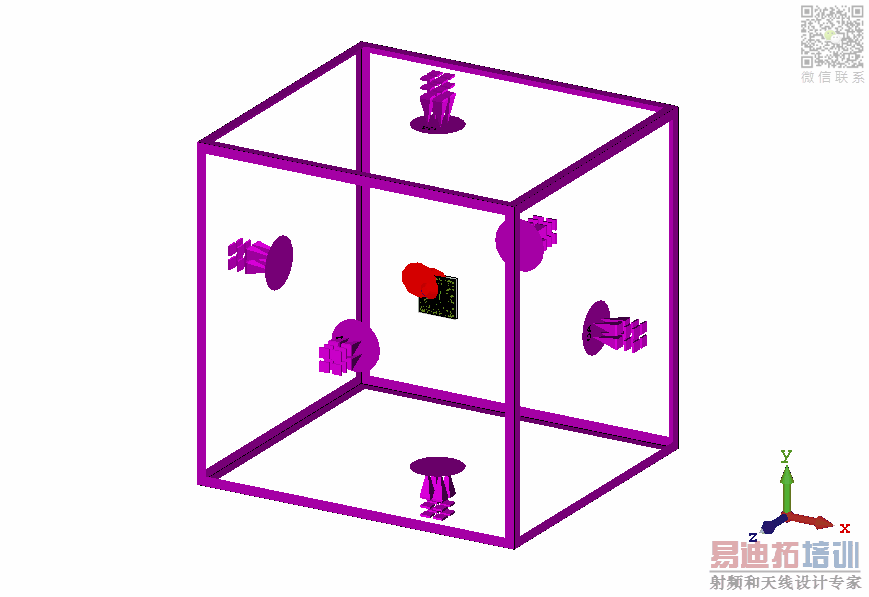

因为仿真的芯片远场辐射,我们需要设置边界条件,如下图所示:

设置探针监视器

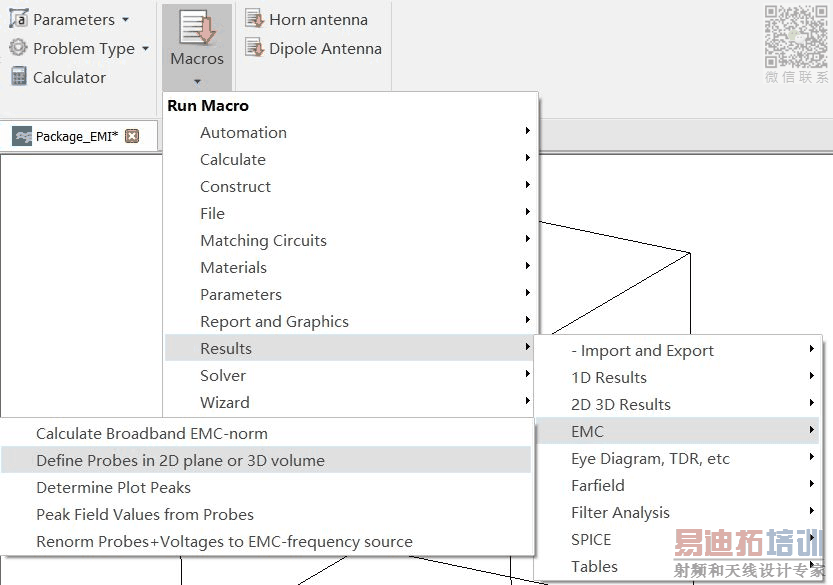

为了观察封装3米远的辐射,我们需要在封装四周设置探针监视器,CST有一个宏能快速设置360°的监视器,Marcos\Results\EMC\Define Probes in 2D plane or 3D volume,如下图所示:

弹出对话框,勾选E-field(farfield),并在3米远的球面上,每间隔30°设置一个监视器,如下图所示:

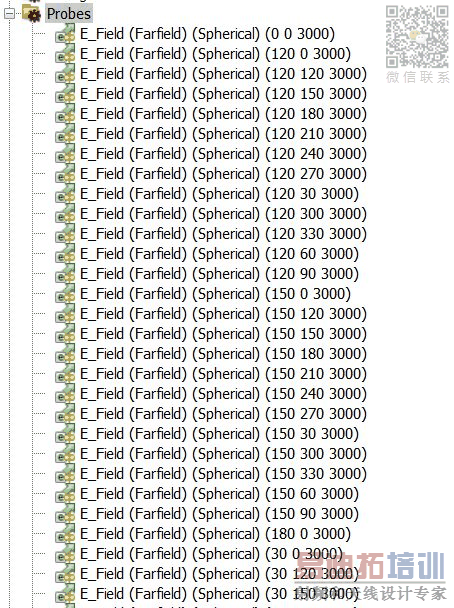

点击左侧导航栏下的Probes,如下图所示:

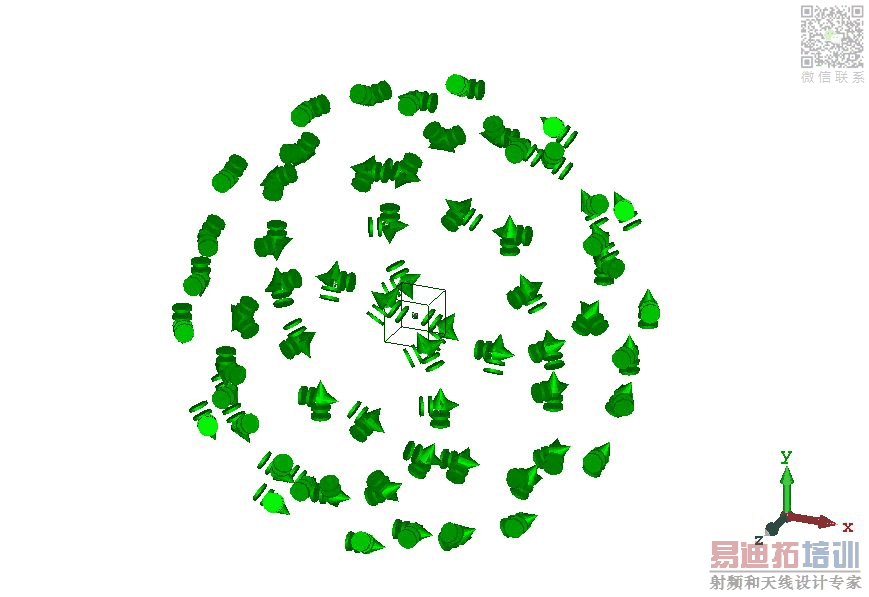

此时窗口主视图,如下图所示:

CST微波工作室培训课程套装,专家讲解,视频教学,帮助您快速学习掌握CST设计应用

上一篇:CST2019中如何将单端转换为差模共模 - CST FAQ07

下一篇:达索系统成功收购德国纯电磁场仿真软件公司CST