- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速 PCB培训手记2(Allegro PCB SI的设计流程)

- Pre-Placement

- Solution Space Analysis

- Constraint-Driven Floorplanning

- Constraint-Driven Routing

- Post-Route DRC

- Post-Route Analysis

Pre-Placement

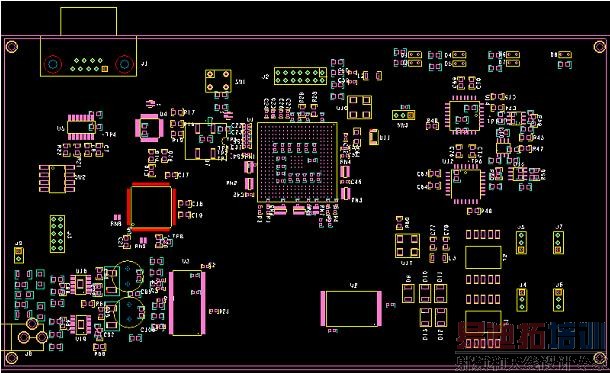

如图 9 所示先将芯片、接插件等按照设计要求预放置在板上。

图 9 预放置

Database Setup Advisor

通过 Database Setup Advisor可以设置板的层叠方式、DC 网络、芯片和接插件的仿真模型等。

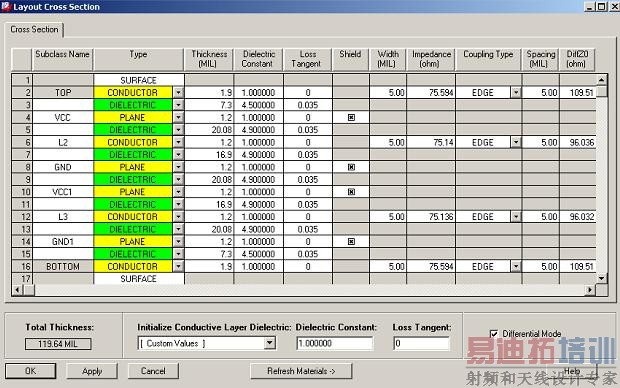

第一步是定义板的层叠方式,如图 10 所示。板的层叠中需设置各层的材料、厚度、传输线的线宽、绝缘材料的介电常数、差分传输线的间距,这些因素决定了各层传输线的阻抗。整个层叠的目的是各层的阻抗要连续,而阻抗的值需控制到 50-75 欧姆的范围内,最好是 50 欧姆。如果阻抗不连续,则需要进一步修改。

图 10 PCB 板的层叠方式

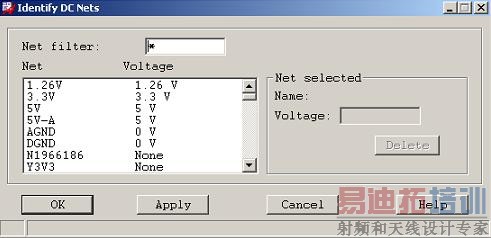

下一步定义 DC 网络的电位,如图 11 所示。

图 11 定义 DC 网络的电位

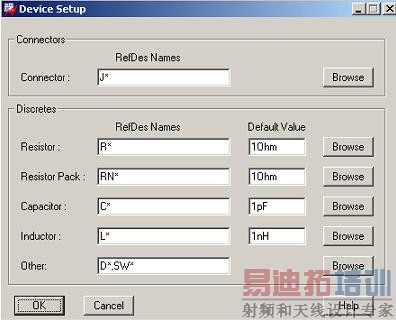

下一步定义分离器件和接插件,这些器件由系统创建仿真 model,如图 12 所示。

图 12 定义分离器件和接插件

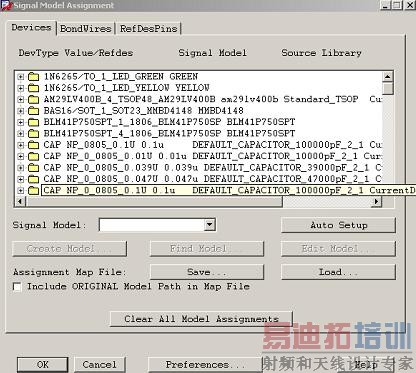

接下来是与仿真关系最紧密的一步,即分配 SI 仿真模型(如图 13),要指定 IC 的 IBIS model,上一步定义的电阻、电容、I/O等可以由系统创建其仿真模型。

图 13 指定 SI model

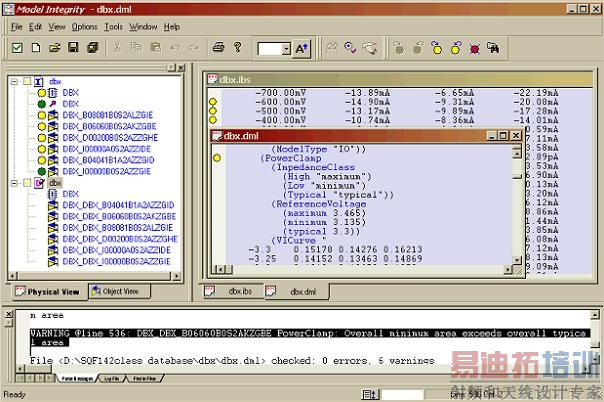

如果芯片厂商提供的 IBIS model 不完整,则需利用 Cadence提供的 Model Integrity进行修正,

如图 14 所示。

图 14 Model Integrity

进行下一步的 SI 审计后结束 Database Setup Advisor过程。

Solution Space Analysis/Constraint-Driven Floorplanning/Constraint-Driven Routing

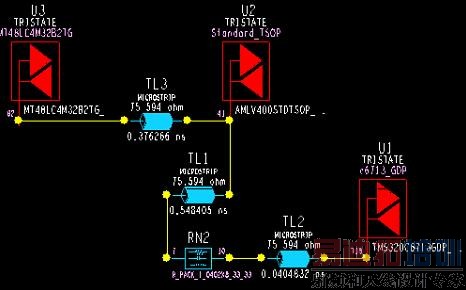

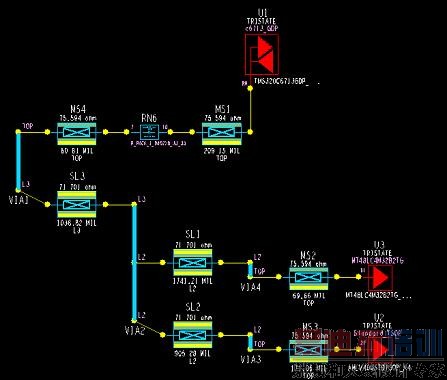

只有完成上述的过程后,我们才可能提取网络的拓朴,尔后进行仿真反射、串绕和定时等的仿真,图 15 是我们利用 SigXplorer提取的 TMS320C6713 数据总线中一部分的拓朴。

图 15 提取拓朴

布线拓朴的不同对信号完整性是有一定影响的。对于一组总线(地址,数据,命令)驱动多达 4、5 个设备(FLASH、SDRAM 等)的情况,在 PCB 布线时,是总线依次到达各设备,如先连到 SDRAM,再到 FLASH……还是总线呈星型分布,即从某处分离,分别连到各设备?布线拓扑对信号完整性的影响,主要反映在各个节点上信号到达时刻不一致,反射信号同样到达某节点的时刻不一致,所以造成信号质量恶化。一般来讲,星型拓扑结构,可以通过控制同样长的几个分支,使信号传输和反射时延一致,达到比较好的信号质量。在使用拓扑之间,要考虑到信号拓扑节点情况、实际工作原理和布线难度。不同的 Buffer,对于信号的反射影响也不一致,所以星型拓扑并不能很好解决上述数据地址总线连接到 FLASH 和 SDRAM 的时延,进而无法确保信号的质量;另一方面,高速的信号一般在 DSP 和 SDRAM 之间通信,FLASH 加载时的速率并不高,所以在高速仿真时只要确保实际高速信号有效工作的节点处的波形,而无需关注 FLASH处波形;星型拓扑比较菊花链等拓扑来讲,布线难度较大,尤其大量数据地址信号都采用星型拓扑时。

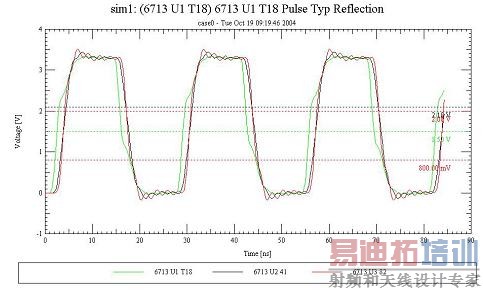

图 16 仿真的信号波形

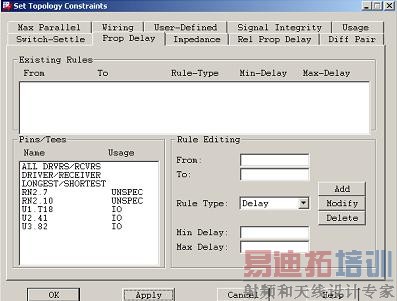

我们可以在 SigXplorer 设置不同的拓朴结构、不同的端接电阻值仿真出信号的波形质量(减缓反射),可以设置不同的平行线长度和间距来仿真获得串绕值并将串绕限制在一定的范围内,并由上述仿真结果获得布线规则,如图 17 所示,这些规则会自动用于指导布线。从图 17 可以看出,规则的种类较多。

图 17 设置电气规则

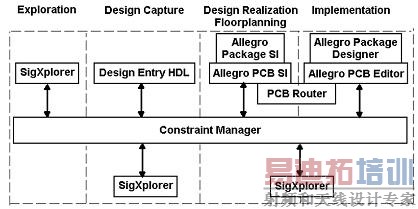

我们发现,整个规则管理的层次结构是跨平台的,体现在原理图设计到 PCB 布线、SI分析的整个过程中(如图 18)。

图 18 规则管理

Post-Route DRC/Post-Route Analysis

在布线结束后,我们可以利用 SI 依次点击菜单 Analyze > SI/EMI Sim > Probe进行后分析,如图19,这时候的传输线模型是真正的有损传输线模型,包括过孔也被赋予其仿真模型,我们仍然可以进行反射、串绕、定时等的分析看布线结果是否真的符合规则。

图 19 后分析提取拓朴

5.Bug

Cadence 的 Allegro SPB 是一套 Bug 丛生的软件。另一套 Bug 丛生的软件是著名的“瘟酒吧”――Windows 98,然而它们都是世界上最好的软件。我们永远在做 1+1 的数学题,哪里会有 Bug?但终究发现,也许最大的 Bug 便是没有 Bug。

没有 Bug 丛生软件的民族是悲哀的。

6.致谢

感谢 Cadence 公司为我们贡献了一个顶级的 PCB 设计软件!

感谢 Cadence 公司资深工程师孙皖平先生的细心指导和李君小姐的热心帮助!

感谢深圳快捷 PCB 制造商的鼎立支持!

感谢不辞辛劳的杨平导师对我们的耐心辅导!

最后感谢我的拍档胡健先生默默无闻的奉献!

宋宝华

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:在Allegro中如何进行设计重用

下一篇:用allegro

布线的优点和缺点