运放输入范围问题,内有电路图和仿真图

录入:edatop.com 阅读:

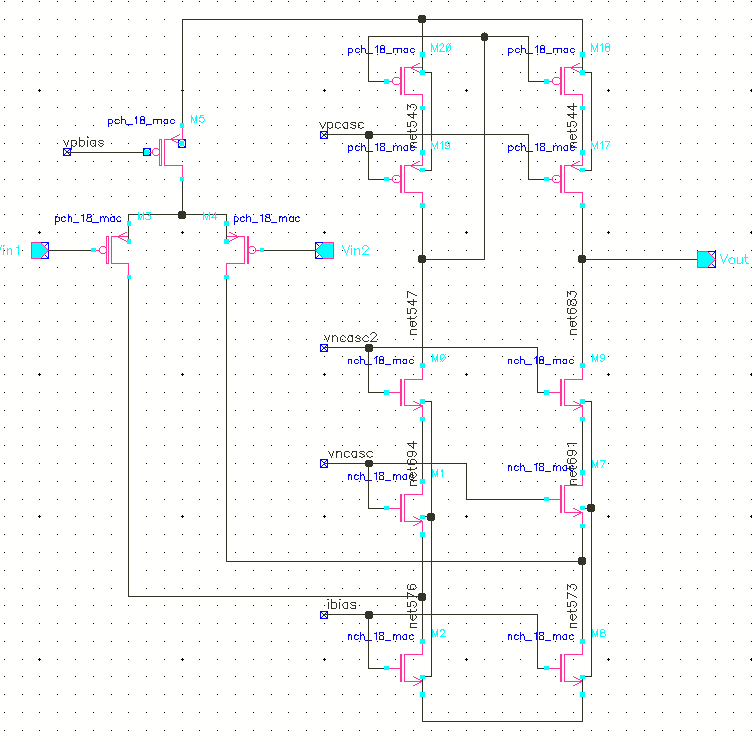

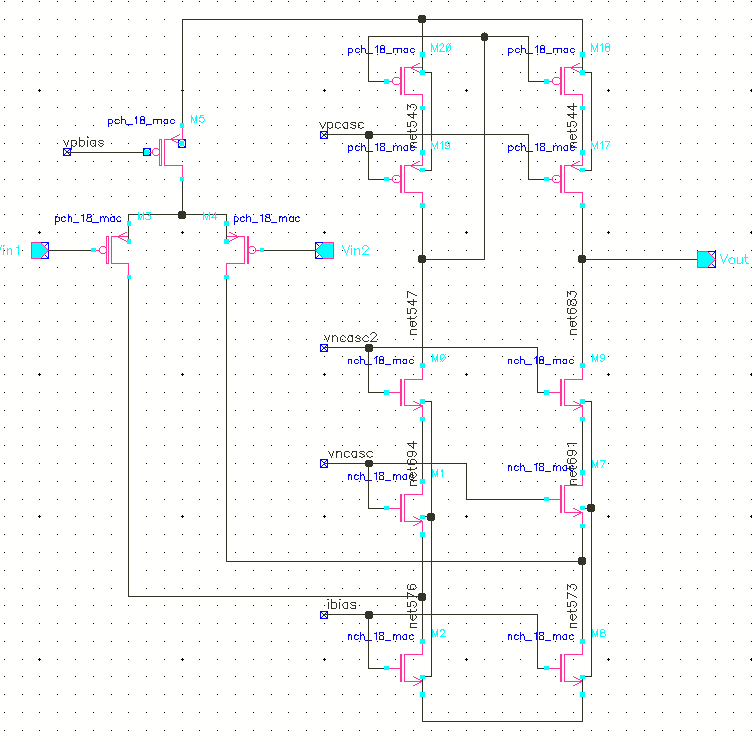

下图是我用在PTAT电路上运放的电路图:

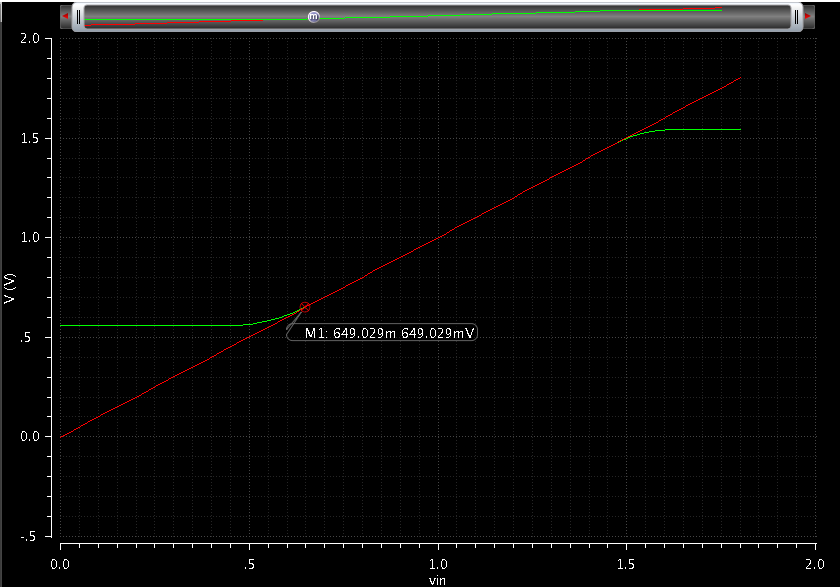

是一折叠cascode OTA,输入为PMOS管,理论上来说应该最低输入电压很低才对,可是在TSMC28nm 工艺下,实际上仿真的时候最低输入范围有600+mv,求问大神们是哪里出问题了?下面是仿真结果图

是一折叠cascode OTA,输入为PMOS管,理论上来说应该最低输入电压很低才对,可是在TSMC28nm 工艺下,实际上仿真的时候最低输入范围有600+mv,求问大神们是哪里出问题了?下面是仿真结果图

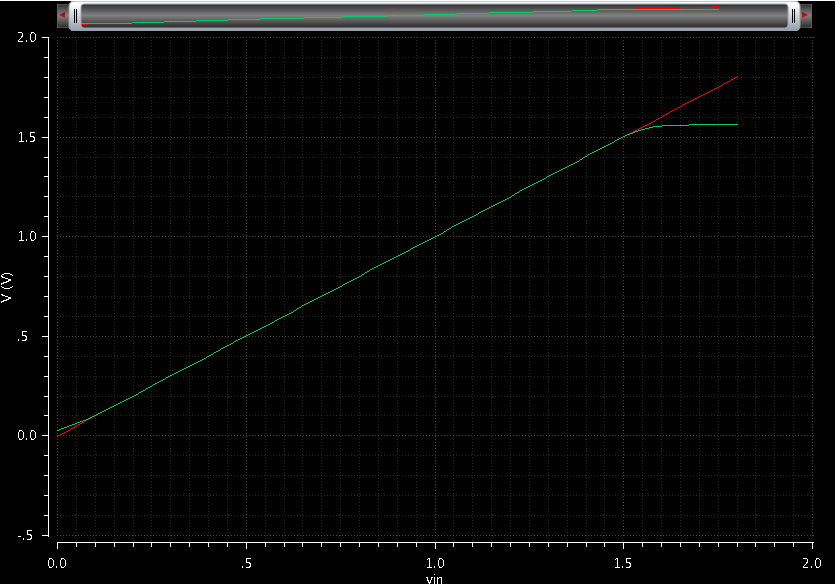

仿真方法是将运放接成跟随器,对同相端电压从0~1.8V进行扫描,测输出电压,红色是输入电压,绿色是输出电压。

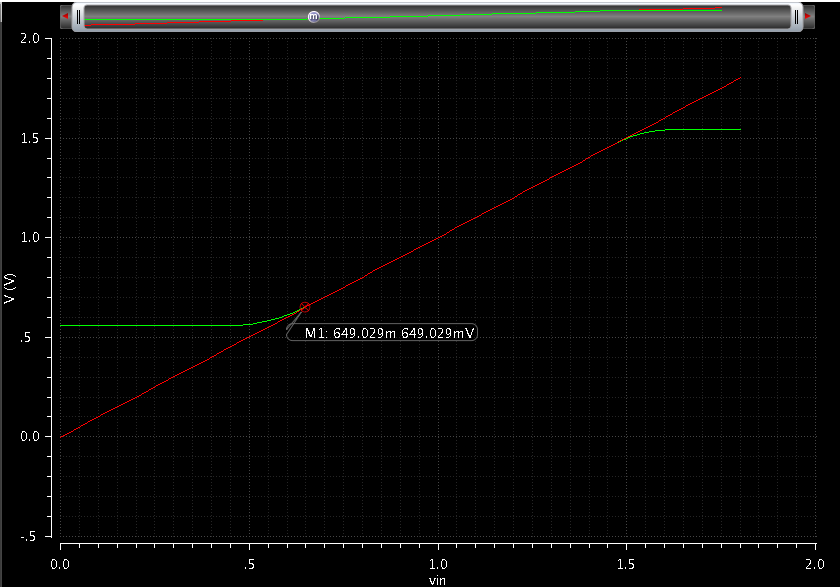

后来又用smic28nm 工艺做了这个电路,下面是仿真结果图,完全没有问题。

仿真方法问题,接成跟随器但是输出有共模电平要求。你输入是0V 输出能输出0V?

所以建议开环来仿真

同意楼上,接成跟随器你的输出共模电平没有去考虑

输出范围有限,所以会有这样的情况。建议调整输出的几个bias。

谢谢!确实是没有考虑到输出范围,我开环仿真了一次,发现确实是收到了输出范围的限制,请问下如何让最低输出范围降下来?

谢谢!确实是没有考虑到输出范围,我开环仿真了一次,发现确实是收到了输出范围的限制,请问下如何让最低输出范围降下来?

谢谢!确实是没有考虑到输出范围,我开环仿真了一次,发现确实是收到了输出范围的限制,请问下如何让最低输出范围降下来?

这种共源共栅的输出范围不大,可以加一级输出级,简单的输出级就用一个共源放大级就可以了

可以双端输出

申明:网友回复良莠不齐,仅供参考。如需专业解答,请学习本站推出的微波射频专业培训课程。

上一篇:高方阻值的poly电阻

下一篇:sigma-delta调制器 信噪比峰值