- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用于下一代无线基础设备的发射机RFIC集成设计

从3G升级到LTE Advance,对下一代移动通信基础设备和器件供应商提出诸多挑战。下一代无线设备要求支持更宽的信号带宽、更复杂的调制方式,以便在全球范围内部署的各种运行频段上都能获得更高的数据速率。因此,噪声、信号线性度、功耗和外形尺寸等性能都非常关键,对这些性能的要求也更苛刻,元器件供应商同样被要求降低成本和尺寸以支持更高密度的应用。

RFIC设计师面临的挑战也将日益艰巨,因为集成的性能需要至少相当或超过分立元器件实现的性能。在采用分立元器件实现方案时,系统设计师可以分别采取不同技术(如GaAs、Si Bipolar或CMOS)进行最优化的设计。但对那些想通过单一工艺技术提供更高集成度的RFIC设计师来说,这种选择最佳工艺技术的灵活性是最大的挑战。

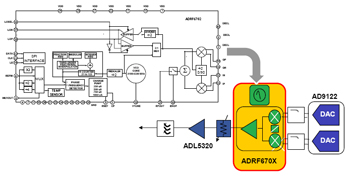

图1:用于2G至LTE应用的基站发射机简化框图。

在基站发送器内,模拟I/Q调制器是决定发送信号路径的本底噪声和线性度的关键RFIC器件,因此不允许任何为了降低尺寸、功耗或成本而劣化性能。

幸运的是,SiGe BiCMOS工艺技术可实现更高集成度而又不牺牲性能。这些工艺通常能提供多种速度类别的SiGe NPN晶体管,在某些情况下还能提供一倍(更多时候是两倍)CMOS晶体管特征尺寸的互补高性能PNP晶体管。在此基础上,还能增加MIM电容、薄膜电阻以及更重要的多层厚铜和铝金属膜。这些特性能够帮助设计师在单芯片上实现多个高性能的功能模块,从而极大地降低功耗和缩小体积,同时保持很高的性能。

发射机板级设计的一个重要方面是用于各个上变频和下变频转换电路的本振时钟的合成和分配。基站本振时钟的分配必须保持到PCB所有远距离位置的相位一致性,而且必须具有低的带内噪声、宽带噪声以及总杂散噪声。混频器性能与驱动它的本振性能一样,因此高质量的本振是提高发射机总体性能的关键。另外,本振信号上很小的相位噪声或杂散分量都有可能在模拟信号路径中引入足够大的能量,并致使发射机不能满足一些主要的蜂窝通信标准(MC-GSM、WCDMA、LTE、WiMAX)规定的杂散干扰指标。这些标准要求的本振频率范围从约500MHz至接近4GHz,这意味着用于本振时钟分配的版图设计必须十分小心。从本振产生到最后终结的走线长度应尽可能短,但如果本振合成器必须馈送到多个不同器件时,这个要求就很难满足。一种解决方案是将公共的低频参考时钟馈送到每个本振附近的独立PLL合成器,但这会占用很大的PCB面积。

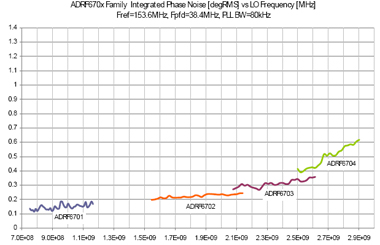

通过集成先进的小数N分频PLL和VCO,ADRF670x 系列集成式调制器解决了上述许多问题。使用硅锗技术能让内置VCO的正交调制器和混频器的动态范围达到业界领先水平,并且具有竞争优势的性能,而体积显著小于外接VCO/PLL解决方案。 VCO在上层厚金属层中实现,可将高Q值的片上电感用作LC电 路的一部分。VCO电容是用MOS开关型MIM 电容组成的,因此允许VCO在宽频范围内切换频率,并具有较低的相位噪声。每次编程 PLL频率时都会自动调整频带,因而能提供独立和可靠的解决方案。在初始化完成后,频带大小的选择要确保器件能在整个温度范围内正常工作。厚金属层还用来集成具有出色反射损耗的输出 巴伦(Balun)。ADRF670x系列由4个频率参数互相重叠的成员组成,覆盖从400MHz至3GHz 的频率范围和频带。每个成员都是根据1dB和3dB通带上的输出巴伦带宽定义的。

图2:ADRF670x中集成的本振相位噪声与本振频率。

ADRF670x和ADRF660x系列小数N分频PLL设计是低相位噪声的3G和4G应用的理想之选。这些新的蜂窝标准具有密集的信号星座,要求越来越低的本振相位噪声以获得足够的性能。传统的PLL合成器设计使用"整数N"架构,其输出频率是鉴相器频率的整数倍。为了提供较小的频率步进,整数倍增因子必须非常大。大量本振相位噪声源于参考路径,并被PLL频率倍增因子所放大,这将导致PLL输出端产生很高的带内噪声。小数N分频PLL允许输出频率有较小的步进,同时保持低的总倍频值,因而与整数N分频PLL相比,可以降低相位噪声放大值。

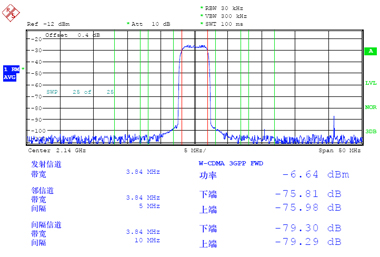

图3:ADRF6702在2140MHz处的ACPR值。

邻信道功率比(ACPR)是判断发射信号有多少泄漏进相邻频带的一个指标。像WCDMA等3G标准对带外发送功率有严格限制。ADRF6702的ACPR指标见图3。调制器提供高度线性的输出功率和低噪声,因此在-6dBm输出点有优于-76dB的ACPR值,这有助于减少调制器后面的增益级数,并使末端功放级电路前面的动态范围达到最大。

ADRF670x系列器件集成了3个LDO电路,可在单5V电源下工作,从而进一步简化了用户应用、减小了成本和电路板面积。LDO用于向VCO、电荷泵以及PLL增量累加调制器提供稳定电源,+5V电源可直接用于e I-Q调制器,以使输出功率最大。

在高密度应用中,ADL670x可以利用PLL完成本振的内部合成,而其它器件可以禁用它们的PLL,并使用来自某个主器件的公共本振。

ADRF670x系列产品设计用于简化用户接口,方便与ADI最新的发送数模转换器AD9122和GaAs放大器(如ADL5320)的连接。(ADL5320是一个1/4瓦高线性度放大器,能够将0dBm以上功率驱动进最末级功放电路。)这三个尺寸紧凑的IC构成了一个完整的有源IC器件组合,是所有下一代多载频蜂窝无线平台的理想之选。

作者:Phillip Halford,产品市场经理 Ed Balboni,RF设计工程师

来源:ADI网站

如何成为一名优秀的射频工程师,敬请关注: 射频工程师养成培训

上一篇:新型RF收发器推动微微蜂窝基站的发展

下一篇:混频器、放大器和振荡器RF术语