对于CF卡的操作(如:读/写),其实就是对CF卡控制器的寄存器进行操作。所以,必须对CF卡的寄存器十分熟悉。这些寄存器统称为任务文件(task file)寄存器:

(1)数据寄存器(读/写),用于CF卡的读写操作。主机通过该寄存器向CF卡数据缓冲写入或从CF卡数据缓冲读出数据。

(2)错误寄存器(读)和特性寄存器(写) 读操作时,此寄存器为错误寄存器,用于指明错误的原因;写操作时,此寄存器为特性寄存器。

(3)扇区数寄存器(读/写)。用来记录读、写扇区的数目。

(4)扇区号寄存器(读/写),用来记录读、写和校验命令指定的起始扇区号或逻辑块地址(LBA)的BIT7:0。

(5)柱面号寄存器(读/写),用来记录读、写、校验和寻址命令指定的柱面号或LBA的BIT23:8。

(6)驱动器/磁头寄存器(读/写),记录读、写、校验和寻道命令指定的驱动器号、磁头号或LBA的BIT27:24,其中BIT6(LBA)用来设置CF卡扇区的寻址方式(LBA=0,采用CHS模式;LBA=1。采用LBA模式)。

(7)状态寄存器(读)和命令寄存器(写),在读操作时,该寄存器是状态寄存器,指示CF卡控制器执行命令后的状态,读状态寄存器则返回CF卡的当前状态;在写操作时,该寄存器是命令寄存器,接收主机发送给CF卡的控制命令。

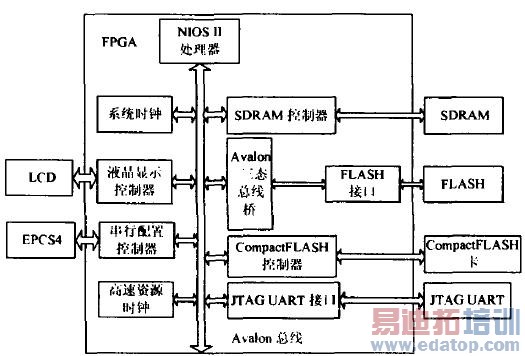

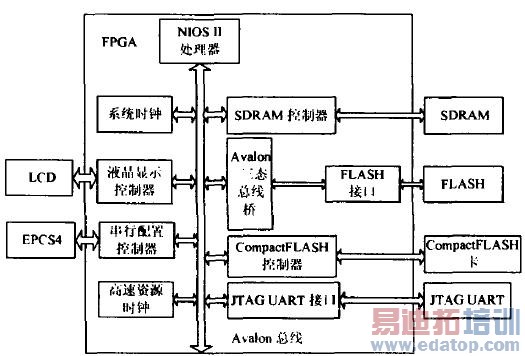

3 Nios II处理器与CF卡的硬件接口设计 在Altera公司提供的SoPC软件中对该软核进行配置时,选用Nios II CPU、内部定时器、CF卡接口控制器、SDRAM 控制器、FLASH 存储器接口、LCD 接口和EPCS4串行配置器件控制器接口。其框图如图2所示。

图2 硬件接口框图 4 CF卡的接口控制器的软件操作

在Nios II系统中,应用软件架构在HAL(硬件抽象层)和C标准库函数上。在Nios II IDE 中建立新的软件工程时,IDE会根据SoPC Builder对系统的硬件配置自动生成一个定制HAL系统库。这个库能为程序和底层硬件的通信提供接口驱动程序,HAL系统库为CF卡接口控制器内核提供了两组直接访问设备寄存器的API函数,其中一个是针对IDE任务文件(ATA)寄存器的,主要提供了对标准的实IDE模式寄存器的访问设,另一个是针对CF接口控制寄存器的,主要提供了对电源,复位,插入或移除检测和中断的控制。设计者只需要调用这些函数就可以访问外部设备。

由于CF卡的读写是以一个扇区为基本单位的。在读写一个扇区之前必须先指明当前需要读写的柱面、头和扇区或LBA地址,然后发送读写命令。一个扇区的512 B需要一次性连续读出或写入。主机读/写CF卡上一个文件的过程是这样的:

(1)CF卡检测。调用:

IORD_ALTERA_AVALON_CF_CTL_STATUS(CF_CTI_BASE)。

(2)CF卡内部控制器向CF卡某些寄存器填写必要的信息。如向扇区号寄存器填写读写数据的起始扇区号或I.BA地址、向扇区数寄存器填写读写数据所占的扇区个数、设置CF卡的扇区寻址方式等。调用:

IOWR_ALTERA_AVALON_CF_IDE_SECTOR_COUNT(CF_IDE_BASE,Sector_cunt);

IOWR_ALTERA_AVALON_CF_IDE_SECTOR_NUMBER(CF_IDE_BASE,Sector_num);

IOWR_ALTERA_AVALON_CF_IDE_CYLINDER_LOW(CF_IDE_BASE,0x00);

IOWR_ALTERA_AVALON_CF_IDE_CYLINDER_HIGH(CF_IDE_BASE,0x00);

IOWR_ALTERA_AVALON_CF_IDE_DEVICE_HEAD(CF_IDE_BASE,0xe0)。

(3)向CF卡的命令寄存器写入操作CF卡的命令。如写操作向CF卡的命令寄存器写入30H,读操作向CF卡的命令寄存器写入20H。调用:

IOWR_ALTERA_AVALON_CF_IDE_COMMAND(CF_IDE_BASE,0x30);

IOWR_ALTERA_AVALON_CF_IDE_COMMAND(CF_IDE_BASE,0x20)。

(4)CF卡有数据传输请求之后,主机读写CF卡的数据寄存器,从而实现从CF卡数据缓冲读出数据或向CF卡数据缓冲写入数据。调用:

IORD_ALTERA_AVAlON_CF_IDE_DATA (CF_IDE_BASE);

IOWR_ALTERA_AVALON_CF_IDE_DATA(CF_IDE_BASE,Data_Write)。

(5)在执行以上操作的过程中,每执行一步。都应该检测状态寄存器,确定CF卡的当前状态,从而确定下一步应该执行什么操作(参考状态寄存器的BIT位的意义,编写检测代码)。调用:

IORD_ALTERA_AVALON_CF_IDE_STATUS(CF_IDE_BASE)。

由于CF卡由ATA控制器和FLASH存储器2部分构成,处理器访问FLASH存储器的速度远远小于访问内存的速度,如果系统频繁访问CF卡,势必会影响系统的实时性和工作效率。所以必须考虑CF卡读写程序的设计技巧 。根据存储器访问的局部性原理,CPU 存取数据所访问的存储单元都趋向于聚集在一个较小的连续区域。

从时间上看,如果一个信息项正在被访问,那么在近期他很可能还会被再次访问。从空间上看,在最近将用到的信息很可能与目前正在使用的信息在空间地址上是临近的。在Nios II硬件系统设计中,添加了片上的存储空间,用于存储最近访问过的扇区数据。另外还设置了两个全局变量:一个保存最近备份的扇区编号;另一个说明备份数据是否与CF卡中的相应数据一致,如果一致,其值为0,否则为1。这样不但可以减少读写CF卡的次数。而且提高了访问速度,通过添加硬件缓冲区,满足嵌入式操作系统的实时性要求。目前,该设计已经在开发板上实现,运行稳定可靠。

编辑:博子

上一篇:多核芯片未充分利用

并行编程无进展

下一篇:低压电力线信道噪声环境下捕获算法的改进

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

国内最全面、系统、专业的手机天线设计培训课程,没有之一;是您学习手机天线设计的最佳选择...【More..】

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

网站地图

|