- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

CMOS电路中ESD保护结构的设计

录入:edatop.com 点击:

摘要:本文研究了在CMOS 工艺中I/O 电路的 ESD保护结构设计以及相关版图的要求,其中重点讨论了PAD到VSS电流通路的建立。

关键词:ESD保护电路,ESD设计窗口,ESD 电流通路

1 引言

静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,Complementary Metal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS, Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

2 ESD的测试方法

ESD模型常见的有三种,人体模型(HBM ,Human Body Model)、充电器件模型(CDM,Charge Device Model)和机器模型(MM,Machine Mode),其中以人体模型最为通行。一般的商用芯片,要求能够通过2kV静电电压的HBM检测。对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

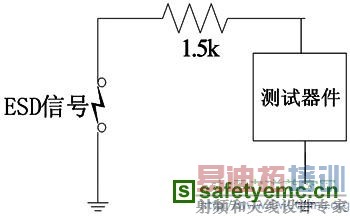

图1 人体模型(HBM)的等效电路。人体的等效电阻为1.5kΩ。

进入芯片的静电可以通过任意一个引脚放电,测试时,任意两个引脚之间都应该进行放电测试,每次放电检测都有正负两种极性,所以对I/O引脚会进行以下六种测试:

1) PS模式:VSS接地,引脚施加正的ESD电压,对VSS放电,其余引脚悬空;

2) NS模式:VSS接地,引脚施加负的ESD电压,对VSS放电,其余引脚悬空;

3) PD模式:VDD接地,引脚施加正的ESD电压,对VDD放电,其余引脚悬空;

4) ND模式:VDD接地,引脚施加负的ESD电压,对VDD放电,其余引脚悬空;

5) 引脚对引脚正向模式:引脚施加正的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空;

6) 引脚对引脚反向模式:引脚施加负的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空。

VDD引脚只需进行(1)(2)项测试

3 ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能钳位工作电路的电压,防止工作电路由于电压过载而受损。这条电路通路还需要有很好的工作稳定性,能在ESD发生时快速响应,而且还不能对芯片正常工作电路有影响。

4 CMOS电路ESD保护结构的设计

根据ESD的测试方法以及ESD保护电路的原理可知,在芯片中我们需要建立六种低阻ESD电流通路,它们分别是:

1) 引脚焊块(PAD)到VSS的低阻放电通路

2) VSS到PAD的低阻放电通路

3) PAD到VDD的低阻放电通路

4) VDD到PAD的低阻放电通路

5) PAD受到正向ESD放电时,PAD到PAD的通路

6) PAD受到负向ESD放电时,PAD到PAD的通路

7) VDD与VSS之间的电流通路。

大部分的ESD电流来自电路外部,(CMD模型除外,它是基于已带电的器件通过管脚与地接触时,发生对地放电引起器件失效而建立的),ESD保护电路一般设计在PAD旁,输入输出(I/O, Input/Output)电路内部。典型的I/O电路示意图如图2,它的工作电路由两部分组成:输出驱动(Output Driver)和输入接收器(Input Receiver)。

关键词:ESD保护电路,ESD设计窗口,ESD 电流通路

1 引言

静电放电(ESD,Electrostatic Discharge)给电子器件环境会带来破坏性的后果。它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,互补金属氧化物半导体(CMOS,Complementary Metal-Oxide Semiconductor)的特征尺寸不断缩小,金属氧化物半导体(MOS, Metal-Oxide Semiconductor)的栅氧厚度越来越薄,MOS管能承受的电流和电压也越来越小,因此要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑。

2 ESD的测试方法

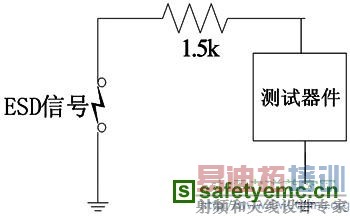

ESD模型常见的有三种,人体模型(HBM ,Human Body Model)、充电器件模型(CDM,Charge Device Model)和机器模型(MM,Machine Mode),其中以人体模型最为通行。一般的商用芯片,要求能够通过2kV静电电压的HBM检测。对于HBM放电,其电流可在几百纳秒内达到几安培,足以损坏芯片内部的电路。

图1 人体模型(HBM)的等效电路。人体的等效电阻为1.5kΩ。

进入芯片的静电可以通过任意一个引脚放电,测试时,任意两个引脚之间都应该进行放电测试,每次放电检测都有正负两种极性,所以对I/O引脚会进行以下六种测试:

1) PS模式:VSS接地,引脚施加正的ESD电压,对VSS放电,其余引脚悬空;

2) NS模式:VSS接地,引脚施加负的ESD电压,对VSS放电,其余引脚悬空;

3) PD模式:VDD接地,引脚施加正的ESD电压,对VDD放电,其余引脚悬空;

4) ND模式:VDD接地,引脚施加负的ESD电压,对VDD放电,其余引脚悬空;

5) 引脚对引脚正向模式:引脚施加正的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空;

6) 引脚对引脚反向模式:引脚施加负的ESD电压,其余所有I/O引脚一起接地,VDD和VSS引脚悬空。

VDD引脚只需进行(1)(2)项测试

3 ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能钳位工作电路的电压,防止工作电路由于电压过载而受损。这条电路通路还需要有很好的工作稳定性,能在ESD发生时快速响应,而且还不能对芯片正常工作电路有影响。

4 CMOS电路ESD保护结构的设计

根据ESD的测试方法以及ESD保护电路的原理可知,在芯片中我们需要建立六种低阻ESD电流通路,它们分别是:

1) 引脚焊块(PAD)到VSS的低阻放电通路

2) VSS到PAD的低阻放电通路

3) PAD到VDD的低阻放电通路

4) VDD到PAD的低阻放电通路

5) PAD受到正向ESD放电时,PAD到PAD的通路

6) PAD受到负向ESD放电时,PAD到PAD的通路

7) VDD与VSS之间的电流通路。

大部分的ESD电流来自电路外部,(CMD模型除外,它是基于已带电的器件通过管脚与地接触时,发生对地放电引起器件失效而建立的),ESD保护电路一般设计在PAD旁,输入输出(I/O, Input/Output)电路内部。典型的I/O电路示意图如图2,它的工作电路由两部分组成:输出驱动(Output Driver)和输入接收器(Input Receiver)。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:下一代电子设备的静电防护和信号完整性

下一篇:ESD电路保护设计中的若干关键问题