- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

探讨电磁干扰和射频干扰及其抑制措施

1、引言

随着电子系统的日益精密、复杂及多功能化,电子干扰问题日趋严重,它可使系统的性能发生变化、减弱,甚至导致系统完全失灵。特别是EMI/RFI(电磁干扰/射频干扰)问题,已成为近几年电子产业的热点。为此,不少国家的专业委员会相继制定了法规,对电子产品的电磁波不泄露、抗干扰能力提出了严格规定,并强制执行。

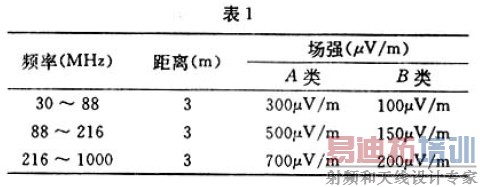

美国联邦通信委员会(FCC)于1983年颁布了20780文件,对计算机类器件的EMI进行限制;德国有关部门颁布了限制EMI的VDE规范,在放射和辐射方面的约束比FCC规范更严格;欧洲共同体又在VDE规范中增加了RF抗扰性、静电泄放和电源线抗扰性等指标。FCC、VDE规范将电子设备分为A(工业类设备)和B(消费类设备)两类,具体限制如表1所示。

此外,还有一系列适用于电子EMI/RFI防护的标准文件:MIL-STD-461、MIL-STD-462、MIL-STD-463、MIL-STD-826、MIL-E-6051、MIL-I-6181、MIL-I-11748、MIL-I-26600、MSFC-SPEC279等,所有这些法规性文件对电子系统的干扰防护起到了重大的作用。本文详细讨论了电子线路及系统中EMI/RFI的特征及其抑制措施。

2、EMI/RFI特性分析

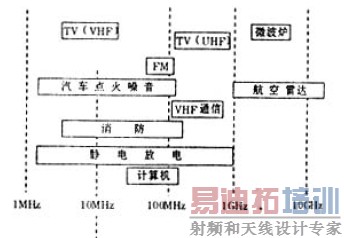

电子系统的干扰主要有电磁干扰(EMI)、射频干扰(RFI)和电磁脉冲(EMP)三种,根据其来源可分为外界和内部两种,每个电子电气设备均可看作干扰源,这种干扰源不胜枚举。EMI是在电子设备中产生的不需要的响应;RFI则从属于EMI;EMP是一种瞬态现象,它可由系统内部原因(电压冲击、电源中断、电感负载转换等)或外部原因(闪电、核爆炸等)引起,能耦合到任何导线上,如电源线和电话线等,而与这些导线相连的电子系统将受到瞬时严重干扰或使系统内的电子电路受到永久性损坏。图1给出了常见EMI/RFI的干扰源及其频率范围。

图1、常见干扰源及频率范围

2.1、干扰途径

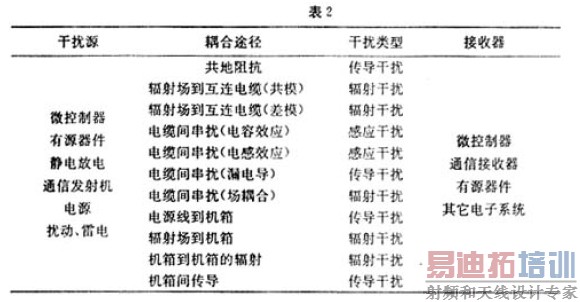

任何干扰问题可分解为干扰源、干扰接收器和干扰的耦合途径三个方面,即所谓的干扰三要素。如表2所示。

干扰信号是通过传导(电路或系统的内部连接,干扰源和接收器由导体连接)、辐射(寄生电感和寄生电容,干扰源和接收器相距大于数个波长)和感应(电容效应与电感效应,干扰源和接收器相距小于数个波长)到达接收器。如果干扰信号的频率小于30 MHz,主要通过内部连接耦合;如果大于30 MHz,其耦合途径是电缆辐射和连接器泄露;如果大于300 MHz,其耦合途径是插槽和母板辐射。许多情况下,干扰信号是一宽带信号,其耦合方式包括上述所有情形。

2.2、EMI特性分析

在电子系统设计中,应从三个方面来考虑电磁干扰问题:首先是电子系统产生和发射干扰的程度;其次是电子系统在强度为1~10 V/m、距离为3米的电磁场中的抗扰特性;第三是电子系统内部的干扰问题。

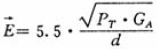

利用干扰三要素分析与EMI相关的问题需要用FAT—ID概念。FAT—ID是描述任何EMI问题固有特性的五个关键因素的缩写,这五个关键参数是频率、幅度、时间、阻抗和距离。实际上,信号的时间响应包含了干扰频谱响应的所有信息。在数字系统中,信号上升时间和脉冲重复率产生的频谱分量可根据下式计算:

将FAT—ID应用于电子系统时,EMI辐射便成为信号上升时间和脉冲重复率的二次函数。

在EMI分析中的另一个重要参数是电缆的尺寸、导线及护套,这是因为,当EMI成为关键因素时,电缆相当于天线或干扰的传输器,必须考虑其物理长度与屏蔽问题。

内部干扰是指系统内部高速数字线路对敏感模拟线路和其它数字线路的影响,或电源噪声对模拟/数字线路的污染。内部干扰通常产生于数字和模拟电路之间,或驱动器与数字线路之间。

2.3、RFI特性分析

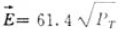

现实生活中的无线电发射源是极其丰富的,如无线电台、电视台、移动通信、计算机、电动机、电锤等等,数不胜数。所有这些电子活动都会影响电子系统的性能。无论RFI的强度和位置如何,电子系统对RFI必须有一个最低的抗扰度。在通信、无线电工程中,抗扰度定义为设备承受每单位RFI功率强度的敏感度。在大多数RFI分析中,用电场强度来描述RFI激励,即

式中E为电场强度(V/m);PT为发送功率(mW/cm2)。

从"干扰源—耦合途径—接收器"的观点出发,电场强度E是发射功率、天线增益和距离的函数,即

式中GA为天线增益;d为电路或系统距干扰源的距离(m)。

由于模拟电路一般在高增益下运行,对RF场比数字电路更为敏感,因此,必须解决μV级和mV级信号的问题;对于数字电路,由于它具有较大的信号摆动和噪声容限,所以对RF场的抑制力更强。RF场可通过电感/电容耦合产生噪声电压或噪声电流。

3、无源元件在EMI/RFI环境中的特性

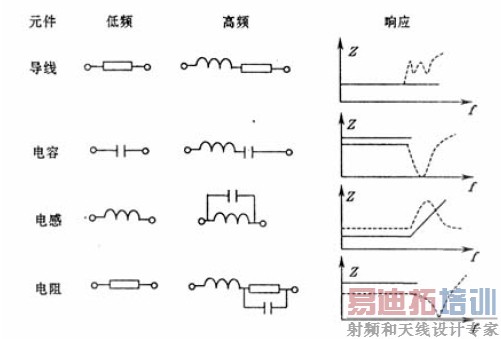

无源元件的合理使用可减小EMI/RFI对电路或系统的影响,对于设计者,应对抗干扰的主要工具--无源元件有足够的了解,特别是它们的非理想作用。图2给出了无源器件在电路中的非理想特性。

图2、无源器件在电路中的非理想特性

可以看出,在很高频率时,导线变成了反射线,电容变成了电感,电感变成了电容,电阻变成了共振电路。在低频时,导线具有很低的电阻(<0.0656Ω/m),但它的寄生电感约为0.079 nH/m,当频率大于13 kHz时,就变成了电感,由于电感的不可控性,最终使其变成一根发射线。根据天线理论可知,无端接的传输线将变成一个具有增益的天线。

4、低通滤波器在抑制EMI/RFI中的应用

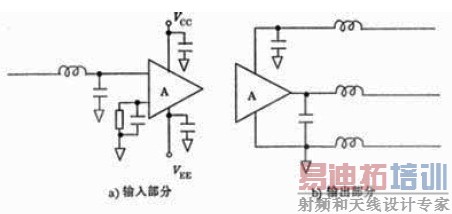

低通滤波器是一种很早就被人们采用的干扰净化技术,对共模和差模噪声有较强的抑制作用。图3所示电路可用于防止模拟电路受EM场和RF场干扰。

图3、模拟电路防止RFI的技术原理

可以看出,干扰的耦合途径有信号输入、信号输出和电源供应三个点,所以采用0.1μF的高频陶瓷电容对所有的电源供应端进行退耦;采用截止频率高于信号带宽10~100倍的低通滤波器对所有的信号线进行滤波。

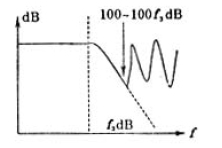

对于低通滤波器,必须保证在预期的最高频率段也是有效的,因为,实际的低通滤波器在高频时会出现泄露现象,如图4所示。这是由于寄生电容引起电感效率的损失,寄生电感引起电容效率的损失所造成的。对于低通滤波器(电感、电容组成),当输入信号频率比滤波器截止频率高100~1000倍时,就发生泄露现象。为此,一般不采用一级低通滤波器,而是分为低频带、中频带和高频带且每个频带单独设置滤波器,如图5所示。

图4、低通滤波器在100~1000f3dB时的效率

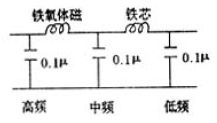

图5、多级滤波器

图5中,低频带宽为10 kHz~1 MHz;中频带宽为1 MHz~100 MHz;高频带宽为100 MHz~1GHz。在低通滤波器中,如果存在任何对地阻抗,该阻抗便成为高频噪声的旁路路径,因此,滤波器的地应是宽频带且连接到低阻抗点或地线层上,以优化滤波性能。另外,高频电容的引脚应尽可能短,最好采用低电感表面贴片式瓷片电容。

5、电源线的EMI/RFI抑制对策

电源线的EMI/RFI是由瞬变电压引起的,因此,这类干扰的抑制对策主要是提高电路或系统对瞬变电压的适应能力。分析和实践证明下述措施对提高电源抗干扰能力是有效的。

(1)在电源引入端加混合电源瞬变保护网络。

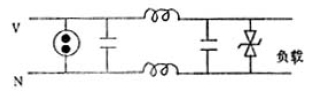

如图6所示,气体放电管和大功率齐纳二极管提供差模与共模保护,在要求不高时,可用金属氧化物压敏电阻代替齐纳二极管。扼流圈用来吸收浪涌电流。

图6、混合电源瞬变保护网络

(2)利用变压器进行隔离。变压器对大于300ns的瞬变有很好的保护作用。但在具体应用中应注意,变压器的连接方式不同,所构成的保护模式也不同。一般由四种方式:1)采用无屏蔽的标准变压器,且次级与安全地相连以消除中性点与地之间的压差;2)采用单层法拉第屏蔽的变压器,屏蔽与安全地连接以实现共模保护;3)采用单层法拉第屏蔽的变压器,初级与中性线相连以实现差模保护;4)采用三层法拉第屏蔽的变压器,可实现差模、共模保护,并能消除中性点与安全地之间的压差。

(3)在电源的整流和稳压输出端除加有大电容低频滤波外,应并接低容量无感高频滤波电容器。其容量:

C=ΔIΔl/Δu

式中ΔI--电源电流波动的峰值;Δl--电流脉动宽度;Δu--电源电压波动允许值。

(4)在每个电路模块上电源线走线在接法上使其终端形成闭环,否则,在电源线终端相当于开路时,高频干扰就会形成全反射,而使干扰信号成倍增加。

(5)尽量使电源线和地线平行走线,使电源线对地呈低阻抗以减小电源噪声干扰。最好使用双绞线馈电。

6、PCB设计中的EMI/RFI保护

印刷电路板上信号线的布设如何,将直接关系到系统对电磁干扰和电磁能辐射的灵敏度,一个不好的PCB设计很可能导致系统的EMC失败。高频噪声在PCB上可能耦合、辐射的途径有:电源线辐射、电源阻抗耦合、公共地阻抗耦合、I/O线的串扰与辐射。因此,在设计中,应从以下几个方面来考虑抑制EMI/RFI。

(1)如果条件允许,应尽可能采用低于实际要求速度的器件。因为,器件速度越高,EMI问题就越严重。对于纳秒级的器件,由于它们具有宽带宽,采样时钟和输入对任何形式的高频噪声都会响应。对于此类高速器件,可在其I/O端采用具有铁氧体芯电感的小型滤波器以降低对EMI/RFI环境的敏感度。如果是双极性供电,应在正、负供电线上均加铁氧体芯电感。

(2)电源层、地线层和信号层的合理设计。一个好的PCB布局应将关键的模拟信号路径与高频源隔离、数字/模拟的高频部分与低频部分相互隔离。采用多层板可减小EMI发射,且对RF场的抗扰度要比双面板增加10倍或更多。比较好的多层板排列是将信号线嵌入在电源层和地线层之间,这种设计的优点是低阻抗、低辐射、低串扰,可减小50MHz以上的辐射和串扰,但板内容量小,退耦困难,嵌入信号线的测试与检修困难。

(3)PCB中走线的特性阻抗。为了防止反射,要求PCB上走线的特性阻抗应满足单向传输延迟时间等于或大于信号上升/下降时间的一半。为此,一般应采用2英寸/ns准则。表3给出了常用数字逻辑基于2英寸/ns准则的走线长度。2英寸/ns准则也适用于模拟电路的走线设计。

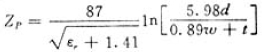

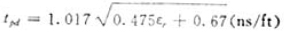

对于利用绝缘材料将信号层与电源/电线层隔离的PCB板的特性阻抗可用下式计算:

式中εr为PCB板材料介电常数;d为各层的厚度(mils);w为线宽(mils);t为线厚(mils)。

信号层走线的单向传输时间由下式确定:

例如:一个标准4层PCB板,一般利用0.021〃FR-4(εr=4.7)型绝缘材料隔离,采用8mil宽、1.4 mil厚的铜层走线,其特性阻抗为88Ω,单向传输时间为1.7 ns/ft。

总之,在PCB设计时,必须按实际情况和可能大些,将信号线间隙用地线填充。电源和地线采用平行走线,有利于减小电感。

7、屏蔽技术

屏蔽技术可防止外部EMI/RFI对电路或系统的影响,但要正确应用屏蔽技术,就必须清楚干扰源、环境、干扰源与被干扰对象之间的距离等问题。如果电路或系统靠近干扰源,电磁场特性取决于干扰源;如果电路远离干扰源,电磁场特性取决于传输介质。当电路与干扰源的距离小于λ/2π(λ为干扰信号波长)时,就认为电路靠近干扰源,否则,认为远离干扰源。

EMI/RFI对电路的影响与其特性阻抗有关,电磁场的特性阻抗(波阻抗)取决于电场和磁场之比。对于远电磁场,其电磁比率就是空气的波阻抗(Z=377Ω);对于近电磁场,波阻抗取决于干扰的固有特性及距干扰源的距离,如果干扰是高电流低电压,则磁场占主要地位,波阻抗小于377Ω,如果干扰是低电流高电压,则电场起主要作用,波阻抗大于377Ω。通常采用封闭导体对电路进行屏蔽,封闭导体对电路屏蔽的有效性取决于屏蔽材料表面对入射波的反射损耗和屏蔽体对内部发射波的吸收损耗。对于电场,反射损耗取决于干扰频率和屏蔽材料,即

适当的封闭屏蔽体对防止外部干扰和限制内部干扰是很有效的,然而,在实际工程中,由于内部电路中的调节旋纽、开关、连接器及通风大呢感原因,经常需要在屏蔽体上开设槽孔,这将削弱屏蔽性能,导致干扰进入系统内部。这种情况下的屏蔽效率为:屏蔽效率

式中λ为干扰信号的波长;L为槽孔的最大长度。

当屏蔽体哂纳感所开槽孔的最大长度等于干扰频率波长的一半时,辐射最大,相当于没有屏蔽效果。为此,在屏蔽体上开设槽孔时,其最大长度要小于干扰信号波长的1/20,同时应在多个面开设而不是在一个面开设槽孔。

8、结论

在日益复杂的电磁环境下,如何减小相互间的电磁干扰,使各种设备和系统能正常运转,是一个亟待解决的问题。在采用不同的方法对EMI/RFI精心抑制时,应分析其综合效应,并对所采用的干扰抑制手段的作用进行恰当的预估,才能获得较理想的效果。

作者:李贵山、杨建平、黄晓峰

9、参考文献

1)、H W Ott.Noise Reduction Techniques in Electronic Systems.Second Editiong.New York,John Wiley&Sons,Inc.,1988

2)、A Rich.Understanding Interference-Type Noise.Ana-log Dialogue,1982,16(3):16~19

3)、A Rich.Shielding and Guarding.Analog Dialogue,1983,17(1):8~13

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:汽车电子MCU的抗EMI设计与测试方案

下一篇:PCB电磁兼容设计要点