- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

微型电感器的简化模式设计

摘要:

考虑了制作微型电感器时可能的构造,通过控制坡莫合金磁心的各向异性或者图样的准分布间隙,用其调节磁导率来达到要求的电感量值。

1引言

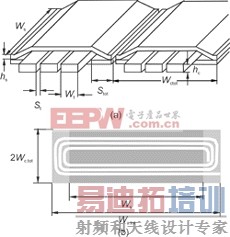

最近,许多文献中提出了采用薄膜磁性材料制造微型变压器的方法,使人们看到了有望采用微制造技术使功率变换器实现微型化。采用薄膜微制造技术能够制造极其精细的图样结构,使其控制涡流损耗,从而可以在20MHz以下采用金属磁性合金。金属磁性合金一般具有较高的磁通密度、较低的磁滞损耗,通过设计及专门的优化,可以达到很高的效率和较高的功率密度。图1中示出了针对分布或准分布间隙电感器的一种设计方法,这种电感器可以用于功率变换电路中。选择脉宽调制(PWM)降压变换器作为说明的例子,其计算方法也可用在其他变换器结构中。

2简化模式的定义

首先分析端匝,其横向宽度Slat需靠近磁心,匝间的横向间隔St可以忽略(见图1)。第一步,计算出单位面积的损耗和控制的功率。假设窗口区的磁场为水平方向,这样,在绕组中的交流损耗可以用一维分析来估算,只要根据导体高度hc和穿透深度δe间的比例进行。可以用交流电阻因子Fr(hc/δc)=Rac/Rdc来描述。对电流波形,可以用傅里叶表达式,对于每个重要谐波K,估算Frk因子。

如果采用各向异性NiFe合金作磁心,主磁通往往可以参照无滞后的磁化轴方向。控制涡流损耗,把叠层磁心淀积成多层膜。对每层和每个磁通密度波形的重要谐波进行损耗估算,并加在一起。作这种估算时,假设磁通密度与各层是平行的。

3简化模式的磁心优化

图1平面电感器近似设计法的示意图(a)和顶视图(b)

可以参考降压变压器应用的设计技术条件,选择:输入电压Uin,输出电压Uo,直流输出峰-峰纹波电流Idc,r=△Ipp/Idc,开关频率ω=2πf。

根据后叙式(9),绕组中的功率损耗可以借助于增加导体高度hc而减小。不过,这种改善是忽略了导体大于2倍穿透深度。作近似分析时,hc可以选择大约1~2个穿透深度。对忽略的因素进行考虑时,可使hc更精确的优化。对于磁心中的功率损耗,层数N的增加几乎可以忽略。考虑制造成本,应当优化N,在此,假设某一个层数。这样磁心的高度可以对最大功率密度予以调节,得出(例如,对该降压变换器应用)表达式

式中,A为“有效的”器件区域,ρs和ρc分别表示磁心和导体的电阻率,D是变换器的占空比,Kcore是计量磁心中谐波损耗的因子,而|a1|=2sin(Dπ)/[π2D(1-D)]是电流波形的第一个傅里叶系数。可变的Bpk为交流磁通密度峰-峰值的一半。对于最佳设计,总的磁通密度峰值应接近(或等于)饱和量级Bsat。因此选择Bpk=Bsat/(1+2/r),这样使Bdc+Bpr=Bsat,对最大功率密度的表达式(1)作为给定系数的函数。

表1对5MHz零电压开关降压变换器的电感器设计实例。[p]

表上部为设计输入参数,下部为输出

符号 | 名称 | 数值 |

|---|---|---|

技术条件 | ||

f | 频率 | 5MHz |

IDC | 输出电流 | 1A |

△IPP | 电流脉动 | 3A |

Uin | 输入电压 | 40V |

Uo | 输出电压 | 5V |

材料数据与技术参数 | ||

N | 磁心叠层数 | 12 |

hsmax | 磁心最大允许高度 | 16μm |

Bsat | 饱和磁通密度 | 1.1T |

ρc | 导体(Cu)的电阻率 | 2μΩ-cm |

ρs | 铁心(80%NiFe)的电阻率 | 20μΩ-cm |

hsep | 纵向分隔铁心 | 15μm |

Wcon | 与铁心接触宽度 | 40μm |

Sres | 光刻胶凸条的斜度 | 5.5 |

器件参数 | ||

L | 需要的电感值 | 292nH |

μr | 设计要求的磁导率 | 490 |

D | 转换器的占空比 | 12.5% |

hs | 磁心总高度 | 12.0μm |

δs | 在5MHz时磁心的穿透深度 | 2.25μm |

Ws | 磁心的长度(参见图1) | 9.2mm |

BPK | 磁通密度波动值 | 0.66T |

σ | 电流密度 | 3.75A/m2 |

St | 每匝线圈的间隔宽度 | 76μm |

Wt | 每匝线圈的等效宽度 | 266μm |

hc | 导体高度 | 54μm |

δc | 在5MHz下导体的穿透深度 | 32μm |

SLat | 靠近磁心的横向宽度 | 534μm |

n | 匝数 | 3 |

Kend | 端匝损耗电阻因子 | 1.29 |

Ks | 由端匝引起的长度因子 | 1.22 |

Kc | 由St和SLat引起的宽度因子 | 2.62 |

计算性能 | ||

isat | 使磁心饱和的电流 | 2.5A |

RDC | 设计的DC电阻 | 101mΩ |

Fr | 设计在5MHz下的交流电阻因子 | 1.05 |

Kwind | 即Pwind=KwindRDCI2DC | 1.82 |

Pwind | 设计绕组中的总损耗 | 183mW |

Kcore | 谐波磁心损耗因子 | 3.62 |

Pcore | 设计磁心中的总损耗 | 136mW |

Wstot | 器件总长度 | 11.2mm |

2Wc.tot | 器件总宽度 | 4.2mm |

| 输出功率 | 5.0W |

| 功率密度 | 10.6W/cm2 |

η | 设计的效率 | 94.0% |

表1中的参数是假设的一个例子。

在上述的最佳设计中,磁心和绕组之间的分布功率损耗,即Pcoreloss/Pwind1oss=2/3。一般来说,只要忽略磁滞损耗,磁心叠层薄到和穿透深度可以相比,电感要求可用调节磁导率来满足的话,则图1构造的平面电感器和变压器,所有的优化设计将保持这个比例。

4电感调整

满足电感要求的一种方法是调整磁心的磁导率,这就产生了一个有利的磁场构造,避免了优化过程中引入的电感抑制。

对优化设计,为了获得要求的电感,需要有效的磁导率

式中σopt(η)是单位导体宽度,在效率为η时的电流密度。对于一个优化设计来说,一旦选定效率η,就完全指定了磁导率μr。

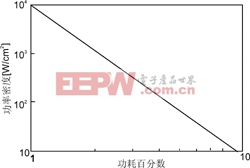

例如,假设表1中的参数,忽略了端匝和其他“无效”间距,以95.5%η98.5%范围设计,则相对磁导率的数值可能在100μr400范围内,如图3所示。对于某一个确定的效率,实际设计一般需要比图3中所示的磁导率要高,这是因为靠近磁心的间距和绝缘匝的间距,在简化模式分析中被忽略了,所以,增加了磁路的长度(见图1)。电感中电流的波形如图4所示。

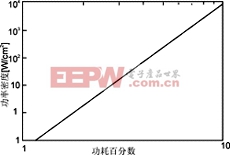

图2叠层数N=12的功率密度与功耗百分数的关系曲线。二座标轴均用对数值,参数已在表1中假设。

图3给定叠层数N=12时的磁导体与功耗百分数的关系曲线。二座标轴均用对数值,参数已在表1中假设,忽略了端匝和其他“无效”区

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:闪存电源原理

分析设计

下一篇:变压器开关电源致命原理