- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

先进互连架构-X架构之介绍与探讨

X架构是第一套大量运用斜角互连线路的量产型IC设计技术,能降低晶片内部20%的互连或佈线资源,并减少30%的贯孔数量。本文将由X架构的市场现况、厂商运用策略以及该架构的绕线与放置等技术原理,探讨此一新架构对IC设计所产生的种种影响。

@内文:在奈米技术下,减少电路互连延迟(interconnect delay)为决定效能(performance)的最关键因素之一,因此设计全程皆需考虑互连的效应,即以互连为导向之设计流程(interconnect-driven design flow),以达成timing closure及design convergence。除此之外,近几年来半导体大厂纷纷投入大笔经费研究新的制程技术,例如铜制程连线技术等等,更突显出了减少电路互连延迟的重要性。

基本上,减少总线长(wirelength)可以同时减少电路互连延迟,但跟最佳绕线距离(euclidean distance)相比,传统上使用垂直绕线(orthogonal routing)的曼哈顿架构(Manhattan-architecture)却可能会增加总线长。为了克服曼哈顿架构的缺点,X-initiative[1]力推X架构(X-architecture)来解决电路互连延迟的问题。

X架构简介与市场现况

X架构是一个使用对角绕线(diagonal routing)的先进互连架构电路。跟传统使用的曼哈顿架构不同,除了前三层使用垂直绕线外,X架构通常使用第四及第五层绕线来作45及135度的绕线,如(图一)。根据报导,X架构平均可以减少20%的总线长及30%的总贯孔数(via),藉此可同时改善晶片效率、功率与成本。而X架构对EDA软件带来的冲击不只是在绕线方面,在平面规划(floorplan)、置放(placement)、时脉绕线(clock routing)等等步骤上也都要重新研究新的演算法来利用X架构带来的好处。

图一 X架构绕线层

X Initiative、益华电脑(Cadence)与东芝即曾联合宣佈,东芝推出第一套採用创新X架构所开发的商用系统单晶片(SoC)元件,?X架构写下重大里程碑。X架构是一套大规模整合的新模式,协助业者制造更小、更快的晶片。东芝最新的TC90400XBG 晶片体现X架构的各种效益,提供一套性能强大、小型化、高整合度的解决方案,支援各种新一代数字影片播放与多媒体家庭娱乐方面的应用。

X 架构是针对晶片中细微互连电路开发的新型绕线法,运用对角电路搭配传统的垂直曼哈顿绕线法。这种创新的架构让晶片内的线路大幅减少,并让SoC元件可使用较少的贯孔来连结各个电路层。X架构创造出更上一层楼的元件效能标准,为新一代数字媒体与其它先进消费性产品带来显着的利益。东芝与益华电脑合作开发X架构,并贊助X Initiative,这个组织已号召超过四十家领导厂商,共同建构产品迈入量产所需的设计链,加速X架构迈入商业应用的阶段。

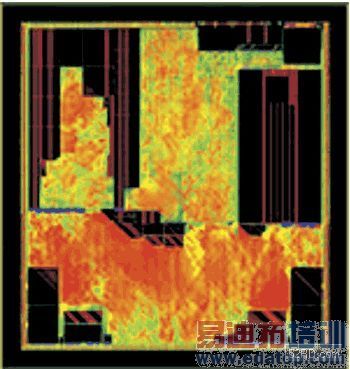

东芝的里程碑晶片TC90400XBG,如(图二),採用130奈米的制程技术,其设计目标是希望能整合在数字媒体与家庭娱乐的系统。相较于采用传统「曼哈顿」设计流程的东芝同级产品,纳入X架构的新晶片能提供加快11%的速度,及体积缩小10%的随机逻辑元件。新晶片的样本于2004年11月推出,预定于2005年第二季开始量产。东芝的TC90400XBG已争取到第一个客户─这款晶片将整合在多款数字电视中,初期将于欧洲市场发表。

图二 TC90400XBG佈线设计图

东芝半导体SoC设计部门技术经理Takashi Yoshimori 强调里程碑对于该公司与X计画皆具有极高的重要性,指出东芝透过与益华电脑及多家X Initiative成员合作,开发出业界第一套採用X架构的SoC。该产品能够满足市场对于效能型单晶片解决方案的多元化需求,发展出比传统设计更快、更小的晶片。而透过这套设计流程,东芝也可进一步巩固在SoC市场的地位。

X Initative创始小组成员暨益华电脑新事业筹画部门技术长Aki Fujimura则表示,东芝在X架构扮演统筹者的角色,加速设计方案迈入商业应用阶段,包括开发第一套90奈米功能测试晶片(在2003年于日本举行的CEATEC消费性电子展中发表)。该公司欣见这项设计架构能成为许多主要设计应用,如数字媒体技术的选择,并认为东芝的产品将为X架构的产品化迈入下一阶段奠定基础,使该架构朝向为全球半导体业界广泛採纳的目标迈进。

以下这篇文章,将继续探讨X架构对绕线及置放的影响。

绕线(Routing)

对角绕线并不是在近期才被提出,在早期对角绕线只应用在印刷电路板(printed- circuit board)上去做平面绕线,而在一般IC上只使用jog来作短距离的对角绕线。而在IC制程技术进步后,对角绕线已经可以完全的应用在一般IC绕线上。因此,现在的X架构一般应用在五层以上金属层的晶片上。为了简化一般standard cell、memory compiler及Hard IP上的绕线,第一到第三层的绕线仍是垂直绕线,而第四、五层才使用对角绕线作全面的绕线。

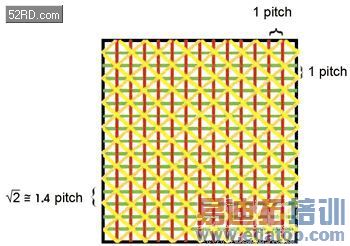

现今大多数的绕线器(router)大多是以格线为主的绕线器(grid-based router),除此之外,大多数的制程在第二到第五层的绕线是使用相同间距(pitch)及线宽(wire width)的,这样做的目的是为了要让贯孔的位置对齐。但是若将第四、五层作对角绕线的话,为了让贯孔的位置对齐,垂直绕线跟对角绕线的交接点必须落在格线上,这样一来,对角绕线间距变成只有(71%)的垂直绕线间距,而违反了最小间距的设计法则(design rule)。而若要同时兼顾接点对齐及最小间距,对角绕线间距需加大到(141%)的垂直绕线间距,如此一来却浪费了可用的绕线空间,如(图三)。因此,若要处理X架构上的绕线问题,最好是用无格线的绕线器(gridless router)来作绕线。无格线的绕线器可以根据制程的设计法则来调整线宽,进而同时兼顾贯孔对齐、最小间距及绕线资源(routing resource)的问题。

图三 对角绕线与垂直绕线间距的关系

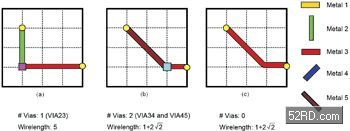

X架构虽然可以减少总线长,进而减少电路连线延迟,但对现今电路连线方面,贯孔的影响也是不容忽视的。一个贯孔产生的延迟,相当于在铝钨制程中50间距的线长,就算是在先进的铜制程中,也相当于有15间距的线长。在X架构上,若大量使用对角绕线的话,可能会造成贯孔的增加。以(图四)为例,图四(a)为在曼哈顿架构下绕线的结果,而图四(b)为在X架构下绕线的结果。虽然图四(b)中的总绕线长度小于图四(a)中的总绕线长度(1+23.828 < 5),但其使用的总贯孔数较多。

为了解决X架构上总贯孔数会增加的问题,先进制程厂便提出了液态绕线(liquid routing)方法来解决这问题。跟传统每一层金属层只能做单一方向绕线的绕线方法不同,液态绕线是指在每一金属层都可以做八方向的绕线,如图图四(c)。藉此,可大大减少总贯孔数,进而改善电路连线延迟所带来的影响。

图四 (a)曼哈顿架构绕线;(b)X架构绕线;(c)液态绕线

接下来以一个真实的晶片为例,在(图五)(a)中为一使用曼哈顿架构绕线的结果,图五(b)为一使用液态绕线作修改过后的绕线结果。在这个例子中,使用液态绕线所减少的总线长达14%,而总贯孔数更减少到40%,这些都证明了液态绕线在X架构下的确是扮演一重要的角色。

图五 (a)曼哈顿架构绕线;(b)液态绕线

置放(Placement)

大多现今的放置器(placer)仍是以垂直线长当作其好坏评断标准。因此,对一个由△X及△Y所构成矩形框(bounding box)的两点连线(two-pin net)而言,放置器会试着去对△X+△Y去做最佳化。虽然在一般曼哈顿绕线架构下,纵横比(aspect ratio)不会影响放置器的好坏评断标准(),但在X架构下,纵横比却大大影响了放置结果的好坏。在纵横比为0的情况下,代表着没有使用任何对角绕线,也就是说线长没有任何的改善;而若在纵横比为1的情况下,代表着完全使用对角绕线,而线长也改善了29.3%。而对于一两点连线的线长改善之期望值如下式:

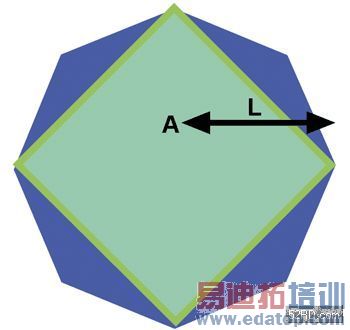

除此之外,我们还可对X架构放置器的线长做进一步的改善。以一个介于A及B两个component之间的两点连线v为例,若v以A为中心,长度为L,那在曼哈顿架构下,B将会落在以A为中心,长度为L的菱型上;若在X架构下,B会落在以A为中心,长度为L的八角型上;如(图六)。

图六 X架构放置器 vs. 曼哈顿架构放置器

由于此X架构放置器的线长是曼哈顿架构的倍,会对效能等造成影响。因此,我们将B可放置的八角型面积缩小成跟曼哈顿架构的菱形一样大,如(图七),来减少放置的总线长,进而改善晶片效能。

图七 X架构放置器之线长改善

结论

X架构是第一套大量运用斜角互连线路的量产型设计技术,能降低晶片内部20%的互连或佈线资源,并减少30%的贯孔数量。在过去20年来,晶片设计一直採用业界标准的「曼哈顿」架构,其名称来自它像城市街道网络般的直角互连线路。X架构将原本曼哈顿架构上第四及第五金属电路层上的互连线路旋转45度。新架构在1至3层上仍旧延用曼哈顿型式,故在单元库(cell libraries)、记忆体单元、编译器、以及IP核心等方面依然保持和现有技术之间的相容性。相信在EDA软体跟制程厂相互配合下,X架构必定能大大改善晶片的效能、功耗及成本。(作者陈少杰为台大电子工程学研究所/台大系统晶片中心研发教授,何宗易为研究生 )