- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

透过FPGA原型验证复杂的ASIC

复杂的ASIC与SoC的验证挑战

今日的挑战,是要在设计实作成硅晶片(silicon)之前,使其需求的功能及完成时间有效化。而在验证过程中令人丧气的主要原因,是因为验证设计需要大量的测试向量(test vector)。由于产品生命週期很短,而市场的机会有限,所以重新编写(re-spinning)一个有瑕疵的ASIC/SoC也不是个好的选择。此外,光罩(mask)的成本动辄超过百万美元,若连工程师的成本也加进去的话,将无法估计。

当ASIC 与 SoC 有显着的差别时,在光罩设计完成(tape out)前创造出一个原型(prototype)的需求仍然是存在的。原型系统最显着的能力是对于能在SoC上执行大量软体内容的需求,以及拥有能够从原始设计中,快速创造衍生产品的能力。这些要求是希望软体工程师在晶片完成silicon之前,能利用原型系统执行侦错(Debug)开发韧体(firmware)以及软体(Software)。

本文主旨在于检验原型如何利用先进的RTL分割技术(advanced RTL partitioning)及RTL除错工具(RTL debugging tool),帮助你用较低的成本,达到预期的成果。明确地说,你可以创造出达到目标的高速度原型板,同时也可以将它复制成多个开发原型板,以较低的成本,让工程师同时完成系统整合以及前期的软体发展。本文叙述的流程,将会完全相容(compatible)大部份的开发板供应商的现货原型。且设计的流程,也能够轻易的以最新FPGA科技做升级。

不同的专家与使用者使用不同的验证策略。本文将讨论以下主题:验证策略、原型的模拟优劣、原型之前需考量到的不同技术议题,兹举Synplicity Certify的原型流程,及使用Synplicity Identify的除错流程为例说明。

验证策略

这个章节将简短地检验多项验证策略,包括模拟、硬体加速、原型设计及硬体模拟。

■模拟法(Simulation)

事件导向(Event-driven)的软体模拟器是较慢的,但当设计区块(design block)小时,其工作状况很好,模拟器提供非常好的除错能力,如同软体的除错功能,有百分之百的可视性(visibility)。然而,即使最快的模拟器在最高阶的工作站里运作,其速度只有大概一秒钟10到30design-clock cycles。对于较大的设计,超过250,000逻辑闸(gates)时,光应用数亿的测试向量(test vector),都会花上数周,甚至数月,非常不实际。即便只运作小部份的软体也很不合理。

■硬体加速(Hardware Acceleration)

利用硬体加速,被验证的设计被烧录(map)至硬体(FPGA序列或是客制化处理器),来加速设计的表现。然而其瓶颈在于测试程式码(test bench)已存在于软体的模拟器。为了加速表现,测试程式码(test bench)也许会被要求要在应用层级沟通(application level),而非讯号层级(signal level)。资料转换为主体(Transaction-based verification,TBV)的验证方法,让测试程式码的互动最小化,以提高表现。加速器(accelerators)主要的限制在于其独立验证设计,并非在系统里进行验证。成本则是另一个需考量的因素,因为加速器无法共用。硬体加速的一般表现大约在200 Hz到100,000 Hz的范围内。

■硬体模拟法(Emulation)

硬体模拟方法可同时烧录(map)设计以及合成测试程式码(test bench) 至硬体,是一个阵列的FPGA或是高速的客制化处理器(custom processors)。你可以在实际系统背景下进行电路模拟(in-circuit mode),验证硬体模拟设计。硬体模拟时除错能力有明显的进步,其表现正常会在1至2 MHz的范围,或是更多(假设有少量非同步设计时脉),且通常在500~600 KHz的范围内执行。当有些低层级诊断软体(diagnostic software)可以在这些速度下执行,系统表现就不足以去发展应用软体。当模拟器可以被分享时,整体成本会非常高昂,约是数十万或是超过一百万美元。高成本让使用多平台(replicates)的想法不切实际,且限制了早期使用者的数量,如软体开发人员和潜在客户。

■FPGA原型验证(FPGA-Based Prototyping)

接下来所叙述的部分,则是将会代表FPGA基础的原型验证(FPGA-based prototyping)。多年以来,FPGA的表现及闸道的容量(gate capacity)有很显着的进步。利用最新的技术,可以map超过一百万ASIC 逻辑闸进入单一FPGA(Altera Stratix ll and Xilinx Virtex 5 家族)。高度自动化的分割工具(Certify)以及除错工具(Identity)已让原型验证更容易实行。低成本(1-3美分/ASIC gate)加上高速表现(超过9 MHz)使得原型验证成为硬体/软体最理想的协同验证(co-verification)方法。有了原型验证,你可以设计自己的客制化开发板,或是向自开发板的供应商购买现货即可。

■为何选择原型验证(Prototype)或硬体模拟(Emulation)?

设计的大小以及复杂度,当设计在光罩完成(tape-out)前,已被广泛的验证及确认。验证复杂的设计极具挑战性,如在数位游戏产业里使用的3D绘图晶片,有许多不同的快取记忆体尺寸或是架构。同样的,验证大型处理器,如IBM用于Microsoft的Xbox 64-bit PowerPc(一亿六千五百万个电晶体或是四千一百二十五万ASIC逻辑闸),亦需要即时的装置来验证。

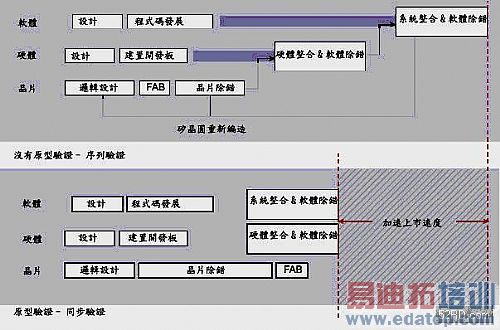

图一 验证阶段表

硬体基础的验证可以提供即时速度及介面让硬体除错,以及硅晶圆在晶圆代工厂到达前,执行软体的能力。图一统整了设计的阶段,以及当硬体及软体同步完成验证所节省的时间。

在了解硬体及软体同步验证的优势之后,下一个重要的问题就是,是否要硬体模拟或是原型验证设计呢?你可以经由比较成本、系统表现、硬体及软体的共同验证、复制或是除错能力等方面来找出最好的答案。

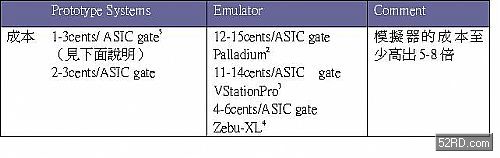

■成本

购买原型验证平台及模拟器的成本有多少呢?这是一个很重要的问题。一个完整的系统(硬体+软体+维护)的成本,可以以一个ASIC逻辑闸多少分(0.01美元)为指标来衡量。下表比较Palladium(Cadence)、VStation(Mentor)及Zebu-XL(Eve)等模拟器,及来自Hardi、PreDesign及Dini集团的原型验证平台。

补充注释

1. 工程成本以及维护成本除外,两种做法里,此两项成本几乎完全相同。

2. Mentor VStationPro:价格从4百万个ASIC逻辑闸需要美金450,000开始。

3. Palladium-Ⅰ:价格从半个基板(约2百万ASIC逻辑闸的容量)美金288,000开始。一个完全满载的Palladium-Ⅰ系统大约一亿两千八百万ASIC闸,费用一千五百四十万美元。

4. Eve-Zebu:Eve有两个家族,UF及XL。UF家族走向原型验证,而XL走向模拟器。

5. 原型验证平台,数家厂商仅提供硬体(如Hardi, Dini)。而其他厂商则提供额外的前端软体 (如ProDesign的ChipIt Manager)。价格范围是可以比较的,当比较类似的硬体时。

a. Dini 新闻发布:2005/10/10及2005/12/9 对Virtex-4 为基础的基板的资料。

b. ProDesign新闻发布:以ChipIt Gold Edition Pro 为基础,两个Virtex 晶片及软体- 美金两万九千元。

c. Hardi新闻发布:以HAPS-31基础,单一Virtex-4 FPGA需要美金八千九百元。

注: Standalone 加速器,例如Tharas Hammmer 及Axis(现为Cadence)并未被考虑,因其有限的科技能力,如同在Section 2.2里的讨论。

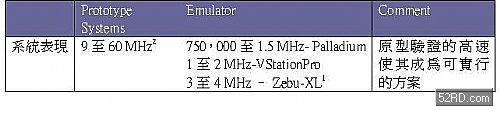

■系统表现 (执行时间)

在系统的背景与即时输入信号(real-time stimulus)下执行设计,系统的表现为关键。下表比较执行时间在原型系统以及模拟器下的表现。表现的好坏,显着地取决于应用程式、设计类型以及非同步时脉的数量。

补充注释

1. 根据EVE的客户来说,设计大小为4百万逻辑闸,其表现被认为,可作为传输基础的验证。

2. 当烧录(map)为单一的FPGA,较高的系统表现是可能的。

例证

对于一个复杂的影像晶片,大约需要650万次循环拨放单一的画面格数(video frame),其需要拨放单格画面的时间(wall clock),当在原型系统下以9.5MHz运作,会得到以下的结果。请注意协同模拟模式下的表现,显着地取决于测试程式码(test bench)的效力,以及设计的结构。

补充注释

1. 模拟器里设计以及系统测试(用于比较系统表现的参考)

2. 设计烧录(map)为原型验证硬体,仅有test-bench(HDLsignal level)在模拟器里

3. 设计烧录(map)为原型验证硬体,仅有 test-bench (C code, signal level)在模拟器里。

4. 设计及合成处理器烧录(map)为原型验证硬体,仅test-bench (C code, 处理器的软体部分)在模拟器里。

5. 设计及test-bench皆烧录(map)于原型验证硬体。

■硬体/软体的协同验证

软硬体协同验证的目标,在于发展诊断、韧体与应用软体以验证系统设计。执行低层级软体(诊断/韧体),通常需求4-6MHz的系统表现(也可以较慢的速度执行,但效率极低)。对于应用层级的软体,通常需要8 MHz或更快的速度。这样的速度在原型验证上是可以达到的,而模拟器(emulator)由于其不佳的系统表现,则被证明为无效率。

■系统复制(System Replicates)

当在原型系统上的设计为稳定且无错的情况下,在设计实作成硅晶片前,软体工程师及潜在的客户/最终使用者需要使用这个原型系统,作为测试以及应用程式的发展。由于原型系统的低成本,你可以创造一个原型系统的”复制品”,将其交给开发者或是客户。而复制模拟器(emulator)在经济考量下,其成本是过高的。

■除错能力

硬体模拟器(emulator)提供极佳的除错能力,因其具有模拟器般的可视性(visibility),但是你必须在系统表现以及逻辑资源作出取捨。在原型系统里,有效的除错取决于供应商的工具,然而经常缺乏需要的可视性能力。当除错工具持续的进步,如Identify暂存器转换阶层除错器(RTL Debugger),原型验证的除错限制因素-可视性(visibility)就变成较小的问题。此外,请注意Debugger只消耗少许(3~10 %)的逻辑资源以执行除错逻辑。

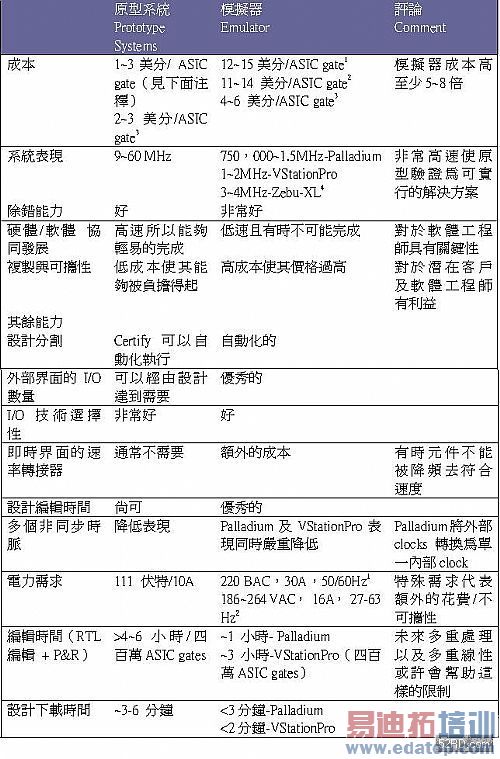

其他需要考虑的因素,包括分割简易化、目标介面的输入输出(I/O)数量、输入输出技术支援、设计的编辑及P&R时间、电力需求等;有关目标介面需求皆列于本文结论的表格,兹简短叙述于下:

■设计分割

这是过程中相当关键的步骤,模拟器(emulator)也已自动化这个步骤。在原型系统里,手动分割一个设计有许多限制,包括了无效率的资源分配。另一个挑战则是当手动执行时,由于FPGA限量的脚位(pins),使其脚位需要多路传输(multiplex)。这些问题在Synplicity的Certify中可以得到解决。

■速率转接器(Rate Adapters)

当与即时输入信号(real-time stimulus)连结时(如RF频率与Spirent测试物运用3G Mobile Station Tester于无线应用或是乙太网路应用),原型系统的高效表现是很重要的。由于低运作速度,模拟器经常需要购买速率转接器介面(rate adapter interfaces),例如Cadence的SpeedBridge(速率转接器能够使低速元件如模拟器与高速元件、测试器或是高速影像资料串流)沟通。在某些案例中,较快的元件无法降低足够的速度以配合模拟器的速度,则使得介面不实用。原型验证的高速排符合了使用速率转接器的需要。

■编辑、佈局绕线与下载次数(Compile, Place and Route & Download Times)

在过去,模拟器要花费6~8小时为一百万个逻辑闸道(gate)的设计做绕线。今日整体时间已有显着的进步。举例而言,四百万个闸门设计的编译(Compile)暂存器转换阶层(RTL)至逻辑闸约一个小时,而下载时包括佈局绕线的时间只要几分钟。若是在原型系统内,执行同样的设计,大约需要花费四到六个小时或更久。

■电力需求

模拟器消耗大量的电力,通常需要在15安培(amperes)下使用220伏特(volts)(Candence的Palladium及Mentor的VStationPro的需求)。这样的需求可转换为额外的成本及维护,且使系统相较之下无可携性。当满载地执行模拟器时,通常需要空调或是冷却设备,并且产生大量的热;原型系统使用标准110伏特,消耗的电力比模拟器少很多,且能够轻松携带,便于在办公室及实验室间移动。

■输入输出(I/O)可取得性

由于目标开发板的设计界面,以及其他副系统在内建电路模式(in-circuit mode)执行时,I/O数目是重要的考量条件。大部分的现货开发板供应商皆有多于足够量的I/O。Palladium-I 有8448 I/Os ,一亿两千八百万个逻辑闸,Palladium-II 有61440 I/Os,而VStation 有4608 I/Os。

■输入输出脚位(I/O Pin)技术

如果你与非常高速的外部讯号做连结(如1Gbps),作为一部分的即时输入讯号,差动讯号技术(differential signaling technology)的支援如LVDS是必要的。你的系统也必须在每个介面连接器下,支援可配置的多重输入输出电压,如5.0,3.3,2.5,1.8及1.5。

从上述的讨论中可以得到结论,模拟器在除错能力(Debug capabilities)、自动化分割(automated partitioning)以及编译(compile)速度有较优秀的表现。然而,原型系统仍有下列显着的优势:

1. 成本

2. 系统表现

3. 硬体/软体的协同验证能力

4. 复制(Replicates)

5. 运用最新的FPGA转移到原型系统的能力

总结上述讨论,可得出下表

补充注释

1. 指Candence Palladium-I 与II

2. 指Metor VStationPro

3. 指Zebu-XL(模拟器) 与Zebu-UF(原型系统)

4. 指Zebu-XL 为了转换基础(transaction-based)的验证的表现

原型验证(Prototyping)的关键考量因素

以下主要是检验部份关键性的考量因素,以达到改善的ROI。在开始实行原型系统前,有一些问题需要询问:

■原型系统成本考量

设计一个高速讯号的PCB本身就可以是一个企划专案。必须要小心考量输出(layout)问题,包含讯号完整性(signal integrity),串音(cross-talk)、阻抗匹配(impedance matching)、对地弹跳杂讯(ground bounce)以及时脉偏移(clock skew)。

1. 讯号需要在原型板上从一个FPGA到另一个FPGA行进,这时必须用最快的速度且用同样的时间行进相同的距离,以维持讯号完整性。举例而言,讯号在数据匯流排上行进,往/返记忆体(DDR2、SDRAM或是QDRII SRAM)必须在相同时间到达终点。

2. 为了分配外部时脉(clocks)至开发板,採用高速时脉驱动器是必要的。直线排列时脉(clock lines)必须被编排,以确定它们同时与所有FPGA一起到达,且须将偏移(skew)降到最低。在高频(超过100 MHz),自动PCB工具并不会投注百分之百的能力在绕线(routing)上,大约有10~15百分比的绕线,需要用手动完成。同样的,考虑到对称地设置全球时脉(global clocks),其中一个方法就是将他们设置在开发板的中央,以最小化偏移现象。

3. 当我们使用多个FPGA开发板时,时脉讯号必须从一个开发板驱动另外一个开发板。因为最后的ASIC设计通常会有多个不同的时脉讯号,因此应该安排多个高速时脉讯号。

4. 开发板上多电压的电力如何分配是另一个重要课题,必须非常小心地去耦合电源层,以防止对地弹跳杂讯。

■ASIC到FPGA编码改变

基本上,ASIC的设计码需要被修改,以烧录至FPGA。闸控式时脉(gated clocks)(减低电量时使用)及Synopsys DesignWare元件必须利用合成工具,在适当的结构下被翻译及重新佈局。Syplicity的Certify及Synplify Premier产品能够自动地管理这个任务。另外一个方面需要考量的是要把ASIC设计的记忆体转换至FPGA的记忆体。FPGA记忆体可能是区块记忆体(Block momory)或是逻辑资源(CLBs/ALMs)。在ASIC设计中,经常有非常广的匯流排(bus),在稍后ASIC设计流程的时期,这些匯流排会分裂成较小的匯流排,同时为了减少电量及符合时序(timing),较小的匯流排可使佈局工具绕线简易化。此外也可以使用Certify 工具的裂解功能(zippering)来处理匯流排。并需要修改Synopsys SDC档案或重新从草图创造档案。

■设计切割

当设计的尺寸过小,或许可以符合单一的高密度FPGA。如果设计并不符合,就必须切割设计为多个FPGA。手动切割有时会很没效率,尤其是採用了尝试错误法(trial-and-error)。当需要手动完成脚位的分配,且脚位的数量大量地增加(例如一个单一的Virtex-4 FPGA有960 I/O),便是另一个冗长乏味的任务。有时经常需要从FPGA多路传输讯号以驱动另一个,之所以提起这个问题,是因为在Synplicity的Certify中,经常因其自动化切割及分配脚位(pin)的能力,而增加许多价值。

■设计除错

现在有了原型系统,只需要在设计中有好的可视性(visibility)以帮助追踪错误,并将其原因与HDL源头的RTL编码建立关联即可。设计师们大部分都对其RTL编码很熟悉,当设计是合成的且烧录至FPGA时,可视性会消失,Synplicity的Identify则可在暂存器转换阶层(RTL)源头层级的除错能力。

■IP整合度

SoC设计经常同时由soft IP(可合成的RTL码)以及hard IP标准元件(Standard components)与外部程式码(bond-out cores),从公司内部或是从第三单位供应商取得。目标是转移所有或大部分的IP,至原型系统的FPGA或子卡(daughter card)中。任何IP在执行软体模拟器时维持原型(model),会显着的减缓系统表现。此时可以考虑利用可合成的转换器(transactors),使用TBV方法论。其目标是将软体模拟器(Software simulator)的交互作用最小化。此外也必须考虑到会用到哪一个匯流排介面(PCIe,AMBA,USB),以及外部记忆体(off-chip memory,如RAM/ROM/Flash等)被放置在开发板或是子卡(daughter card)上的情况。

■IP安全性

在提供原型复制品给潜在客户的情况下,若想要确定发展的IP是安全且加密过,Synplicity有能力加密且安全地转移设计。

■软体除错器的关联介面

当发展软体(诊断、韧体以及应用程式)时,需要建立设计/处理器的介面给第三单位除错器,如Motorola Metrowerks、TI Code Composer、Green Hill Probe或是ARM Muti-ICE/RealView,这些都取决于处理器,此时也要了解能在目标元件上调整到多慢的速度,并保证除错器仍能发挥预估的功能。

■即时元件的关联介面

哪些其他元件会需要关联介面以提供即时输入信号?这些都取决于应用程式,并可能得连接至第三单位的测试器,举例来说,在3G无线应用,可能会连接至Spirent 测试产生器3G MST(Mobile Station Tester)。除了必须了解RF输入信号至你的原型系统的特殊的连接器/电力需求,在输入讯号上也可能需要类比跟数位间的转换,反之亦然。

■原型复制

原型验证的其中一个主要优点,为能够提供软体工程师及潜在客户,对于原型开发板有较早的存取使用。早期存取可以使软体工程师拥有提前开始进行软体除错的机会,并且允许客户利用他们的系统测试IP。当设计的除错仍在进行时,便可以创造复制的原型开发板。

■再利用性

对于未来的计划,能再度使用原型系统的能力是重要考量因素。如果你正在设计自己的开发板,不要妥协于系统表现,或是耗费太多的努力在创造客制化子片(custom daughter cards)的再利用性。现货的开发板也许是可规划配置的(configurable)。

■输入输出无障碍(I/O Accessibility)

当使用多重FPGAs与次系统(sub-system)元件,如:记忆体、匯流排介面、A/D与D/A转换器,以及客制化逻辑时,需要大量可用的I/Os。更重要的是,必须具备容易重新配置在高速连结器中I/Os的互动能力,而此项能力将帮助在较高速中FPGA容量(最初开始需要除错的设计),之后,一旦设计完成,新增的I/Os将可供给外部介面使用。

■配置原型开发板

为了配置设计,或许得用到一个JTAG连接,或是一个与Compact-Flash连结的介面。使用Compact-Flash的优点在于可以储存多种设计,并同时拥有两种选择,因为必须要JTAG替软硬体除错

利用Synplicity’s Certify软体进行原型验证(Prototyping)

在前文已经讨论过部份原型验证前的议题,此时或许你已经准备好将暂存器转换阶层(RTL)设计,烧录到自行设计或是向供应商採买的的原型验证系统(Prototyping system),对于一个多FPGA的开发板来说,第一个问题是如何将系统分割(Partitioning)并映射到(map)到不同的FPGA上!

基于以下几个理由,手动分割一个系统将是令人气馁的工作。即便只是要分割到两块FPGA上,当第一次开始烧录设计时,就必须估计与猜测哪些设计区块适合放到其中一个FPGA,而哪一些区块则适合放到另一个。这些估计无法被证明是合理的。在多数的案例中,更大的问题是,这些逻辑的输入输出信号所需要的脚位,可能需要比这个FPGA可用的脚位更多(被Rent’s rule限制住)。这样的局面暗示着必须牺牲效能,以手动的方式将信号利用多路传输(multiplex)的方法将信号整合。

对应装置的输入输出,是为了维持需求的效能水准,因此必须重复地复制某些逻辑闸。如果有数个区块,而且必须分割到三个或以上的FPGA上头,那么排列的方法之多,将无法管理。试着想像手动所产生多个FPGA间的连结工作(举例来说,一个Xilinx Virtex-4 有960个使用者输入输出脚位)吧!因此对设计者来说,真正需要的是自动化这个程序并移除猜测性的工作。此外,也必须有能力对于一个被指定的暂存器转换阶层(RTL),快速估计出逻辑闸使用和输入输出资源分配,自动多路传输是必要的。Synplicity的Certify将可以处理这些手动且错误倾向的方法,并自动且可靠的完成这些步骤。

■自动分割与合成多颗FPGA设计

Synplicity的Certify暂存器转换阶层(RTL)工具,是一个以多颗FPGA为基础的原型验证系统的分割与合成工具。大多数现成的多FPGA原型验证系统开发板供应商,都将相对应的开发板描述档案和开发板一起出货,这个档案定义了开发板架构并且用作Certify软体的输入。Certify支援Verilog、VHDL和混合语言设计。Certify流程的第一步是转换以特殊应用积体电路(ASIC)导向设计的程式码成为适合FPGA的程式码。

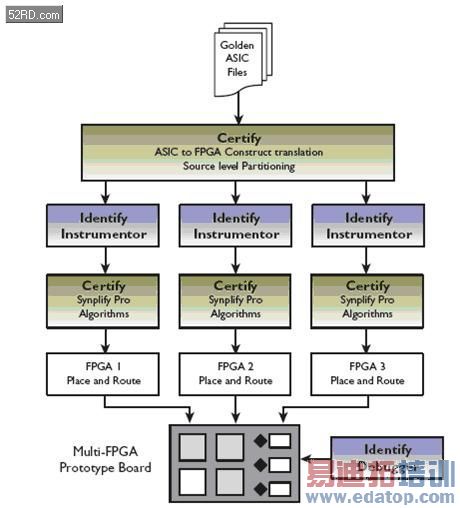

举例来说,gated clocks将会被转换成gate-enabled flops,且Synopsys的DesignWare单元会被转换成同样功能的FPGA架构。在本例中,现成的多颗FPGA原型验证开发板被使用,只要点选一个下拉式选单,列出由其他供应商所提供的开发板,以确定使用正确的开发板定义档。对于客制化的开发板来说,Certify工具有能力创造出一个虚拟的多颗FPGA开发板定义,并在其后的使用中逐渐建立真实的环境。此外,Certify软体亦可用于自动分割设计到多个FPGA(图二)。

Synplicity的硬体描述语言分析工具(HDL Analyst utility)紧密的和Certify软体整合,这套工具可以自动产生与IC制程无关的图形化概观,与高阶的阶层化区块图,以及对应的合成后抽象化电路图(schematics)。

图二 使用Certify与三个FPGA的多FPGA原型验证流程

除了多样化的设计概观之外,Certify软体也提供原型验证版的FPGA图形化的表示法。每一个虚拟的元件都有两个相关的量测数值,一个反映了这个装置的输入输出的使用率(Utilization),而另外一个则反映了面积与资源的使用率。基于软体有FPGA输入输出脚位使用率与资源使用率的资讯,以及FPGA间的绕线(routing)资源资讯,Certify软体可以自动的执行脚位指定(pin assignments),还可以利用QPT快速分割技术(Quick Partitioning Technology)分割设计。简单利用拖曳区块来完成初始的关键区块手动置放之后,QPT就可以说是自动完成了分割所剩区块的冗长琐事。

Certify工具的另外一个效用则是分析分割结果,并提供使用者一个使用CPM(Certify Pin Multiplexing,针脚多路传输)的机会。这可以整合多个信号以减轻装置的输入输出负荷,至于另一个效用,则是当一个分割的可能选项被实现的时,这个实现过程可以被命名且储存,在当成一个之后分割最佳化的起始点,以提供使用者维护与操作多个分割的方案。

一旦分割被执行,这套Certify软体将会合成对应到各个FPGA上头的暂存器转换阶层(RTL)程式码,Certify软体使用一套和Synplicity’s Synplify Pro FPGA合成引擎相同的合成技术。Certify软体包含了资源共享、暂存器平衡(register balancing)、复制(replication)与重新合成(re-synthesis)等先进合成能力。

Certify将不同的FPGA视为设计阶层中额外的一层,这样的方法表示这套工具提供了独特的能力去将时序路径(timing paths)最佳化以提升效能,即使这些路径跨越多个FPGA也一样,。Certify软体也提供时序报告让设计者可以在硬体被程式化之前,即可预知该原型模拟所达到的效能。

■利用Identify Debugger设计除错

当一个FPGA系统在即时介面与时脉速度运作时,去了解在FPGA里头发生什么状况是相当重要的。逻辑分析仪提供精密的触发(triggering)选项,但是触发并不是设计用于捕捉FPGA内部的事件,只能操作在与外部针脚相连的节点(node)上。至于探测能力则是被装置的可用针脚数以及开发板的针脚数所限制住,因此利用逻辑分析仪进行FPGA设计的除错,是相当耗时、受限又不完整,在嵌入式逻辑分析仪中,工程师也同样面临了最所熟悉的问题:「必须理解FPGA内部之中的错误与暂存器转换阶层(RTL)程式的相关性」。

Identify除错软体允许直接在RTL程式对设计量测并除错,这项能力在除错中非常关键,因为设计者多半是对暂存器转换阶层(RTL)程式熟悉,而非逻辑闸阶层电路(gate-level net list)。

■Identifier暂存器转换阶层(RTL)除错流程

Identify包含两个工具: Identify Instrumentor还有Identify Debugger。Identify Instrumentor 用于设定查看点(watch point_与中断点(break point)与控制何时资料该被收集与储存。当一个设计被量测时,侦错点和控制逻辑会被合成以及佈局与绕线到FPGA装置中,步骤完成后Debugger将会被用来直接检查FPGA的结果。

■自动探测(Automated Probing)

Identify软体使用图形化介面,导览所有设计阶层并直接把探针(Probe point)加入到硬体描述语言的原始码(图三)。

直接量测让设计中的信号名称改变可被忽略,因为探针的连结依旧存在,即使名称在实现过程中改变,连结依旧存在而且是以原来的名称显示。利用RTL原始码控制除错流程是Identify工具一个关键优势。Identify Debugger让你可以在设计阶层(RTL)控制并显示除错的结果,亦可以直接显示在暂存器转换阶层(RTL)上,或选择以波形观看器(waveform viewer)显示。

Identify支援multiple IICE(Intelligent In-Circuit Emulator)instances利用以多个非同步时脉触发的逻辑,并观看多个不同的clock domains中的节点,讯号以图形化的方式被标记为探测点。旁边的文字视窗则显示了设计层级,作为组成部分、模组、程序,以及假如(IF)宣告在原始码中被标示行号,以让设计者更容易找到设计的某个部分。在设计阶层中选择一个点将会在隔壁的视窗中显示文字。

图三 Synplicity’s Identify Instrumentor

从硬体描述语言观点来观察设计,监看点和中断点被加入到量测中。设计的探针以各自的色彩标记显示。除了探针外,Identify Instrumentor通讯模组到设计中来传输样本资料,经由JTAG埠,输出到个人电脑上头的波形观看器。探测点可以提供资料来显示或样本触发(sample triggering)。一个设计在被量测之后,将会被合成与编译来提供FPGA工具佈局与绕线。设计的量测绝对无法影响一个设计的功能上的行为,并且通常只佔用大约百分之一到五(有些案例中会更多)的逻辑资源。

■设计除错

一旦设计被量测与实现,Identify Debugger工具就被用来检查设计节点在系统运作下的速度下的行为。当观测点被取样的时候,Identify Debugger被用来开启被量测的逻辑。观测点探针可以被移动到节点与节点之间,在设定完成除错取样与控制信号后,Identify Debugger被用来收集缓冲区(Sample Buffer)取样资料。取样资料是根据取样时脉(Sample clock)来取样,资料样本将被显示到波形观看器或是是在RTL上。一个独特的cycle指标可以用来移动时间的前后,并且当cycle指标移动时,取样值重新根据cycle指标取样并显示在RTL程式上。当然,这些取样资料也可以被转换成标准的VCD档案格式,并且显示在一般的波形观看器上。

Identify Debugger触发机制是运用在暂存器转换阶层(RTL)的控制流程宣告(control flow statement),例如IF、WHEN、CASE以及其他宣告。这些宣告被Identify Instrumentor指定为中断点,让节点在程式码执行中被孤立与监看。这些中断点在暂存器转换阶层(RTL)显示成为程式左边的控制按钮。设计者可以在除错过程或是设计运算中动态的开启或关闭这些中断点。另外一个触发机制是使用设计信号或是匯流排当作触发或是资料取样,中断点(Break point)和观看点(watch point)可以同时被使用。也许最强而有力且有弹性的触发方式是状态机(state machine),设计者可以根据需求在Instrumentation阶段设定需要多少状态(State)来组成状态机(State machine),之后在侦错阶段设定这些状态(State)和状态转换条件(State transition condition)来进行触发(Trigger)。

总结

为确保一个复杂的积体电路(ASIC)或是系统单晶片(SoC)设计可以在短时间内切入市场,创造一个高速运作的原型验证硬体,来侦测硬体中少发生的事件,该需求已经与日剧增。一个在选择原型验证或是硬体模拟的评断重要标准是:成本、执行时间、软硬体协同模拟的速度需求、除错能力、创造低成本复制以提供软体工程师和潜在客户的能力。

为了达到这些标准,很清楚的可以达到最具成本效益的技术是採用以FPGA为基础的开发板。无论是设计自己的客制化原型验证开发板,或是从Synplicity合作厂商中取得现成开发板,Certify和Identify等除错工具都可以节省数个月的验证时间。一个设计团队可以从装置或是系统层级测试真实的硬体,并在初期的设计阶段就发现难以发现的错误。因为硬体可以在早期复制进行软体开发,并且提供潜在客户进行系统整合,市场切入时间可大幅的提前,而且具有完整可视性又容易使用的硬体除错功能更是关键。Identify软体可以让你直接在暂存器转换阶层量测与除错。因为设计者对暂存器转换阶层原始码较为熟悉而非逻辑闸层级的电路,这对于除错来说是另一个重要的关键能力。

简短来说,原型验证的好处是:

1. 低成本(较硬体模拟低五到八倍)。

2. 高效能(9-60MHz)-软体工程师可执行诊断,韧体,或是应用软体。

3. 软/硬体共同验证能力。

4. 复制性-提供多位工程师及潜在客户验证设计。

5. 加速上市时程。

6. 快速地转移原型验证制程到最新版FPGA。

本文章来源自 EEDesign电子设计资源网

附上网站连结:http://www.eedesign.com.tw

未经授权同意请勿擅自转载或节录。

上一篇:谈智能型视频监控

下一篇:浅谈全差动式音讯放大器技术