- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SoC用混载存储器设计技巧

影像、音响处理用系统LSI(SoC: System on Chip)的功能提升,造成晶片内部存储器的容量大幅增加,一般认为如果持续使用传统SRAM,未来势必面临晶片面积大型化与消费电力暴增等问题。为彻底改善上述问题,研究人员应用内建存储器的优点,配合实际用途积极开发SoC用混载存储器,因此本文要介绍SoC用混载存储器的大容量、低消费电力用DTM(Direct Tunneling Memory)、低消费电力非挥发性存储器FRAM(Ferroelectric Random Access Memory)、高速大容量、非挥发性存储器MRAM(Magnetoresistive Random Access Memory)的最新技术动向。

发展经纬

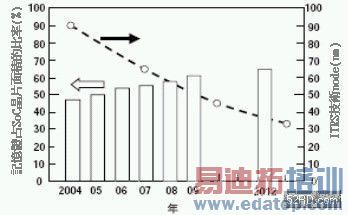

图1是ITRS(International Technology Roadmap of Semiconductor)发表的蓝图(Roadmap)中,有关存储器占SoC晶片面积的比率统计资料。存储器的容量随着用途不同,存储器的平均使用范围大约占晶片总面积的一半左右。

此外微细化技术指标亦即技术节点(Technology Node),平均每隔三年比前世代缩小70%,单位面积的电晶体搭载数量则呈倍数增加,由于存储器占SoC晶片面积比率的增加,使得存储器容量的增加有超越技术节点的倾向(图1)。

图1 存储器占SoC晶片面积的比率与ITRS技术node发展趋势

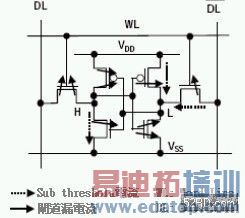

如图2所示传统SoC的存储器6T-SRAM是由6个电晶体构成,其中逻辑电晶体负责SoC演算处理,该电晶体具备高速、不需追加专用制程等特点,属于高使用存储器,反面缺点是6个电晶体才能构成1位元(bit),单位bit的cell面积非常大,不适合大容量化。

随着半导体制程微细化,以往具有低消费电力优势的SRAM,它的漏电电流增加、软件错误率上升、噪音限界(noise margin)降低等问题也逐一表面化,一般认为可以取代6T-SRAM的新世代存储器,必需具备下列列特性:

⑴低单位位元面积,可大容量化。

⑵低追加制程、低制作成本。

⑶可高速读写。

⑷低消费电力,尤其是电源切断时具有保存资料的非挥发性。

⑸抗软件错误率(soft error)。

⑹动作电压与1.0~1.2V的逻辑电晶体相同(或是接近)。

表1是可以达成以上特性的混载存储器的特性比较。事实上在单体记忆IC之中,DRAM与快闪(flash)存储器已经形成非常庞大的市场,而SoC用混载存储器则同时使用DRAM与快闪存储器两种IC,其中DRAM除了朝制程微细化方向发展之外,为维持电容容量DRAM正积极朝立体化方向发展,其结果造成制作技术更加复杂;至于快闪存储器本质上它的资料改写次数只有106次左右,因此快闪IC主要应用集中在类似快闪微电脑等,几乎不需要改写资料特殊领域。

图2 6T-SRAM电路

表1 混载存储器的特性比较

DRAM: Dynamic Random Access Memory

FLASH: Flash Memory DTM: Direct Tunneling Memory

FRAM: Ferroelectric Random Access Memory

MRAM: Magnetoresistive Random Access Memory

DTM存储器的技术动向

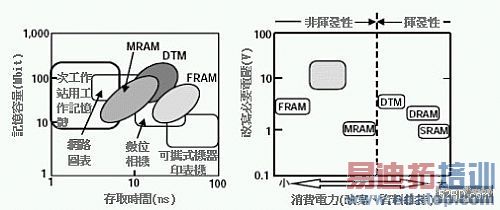

图3(a)是有关混载存储器的存取时间,与记忆容量以及主要用途发展趋势,由图可知5ns以下高速存储器通常使用SRAM,至于10~50ns等级的混载用存储器,只能寄望新世代存储器的出现。

图3(b)是有关存储器的消费电力与改写必要电压特性。虽然非挥发性存储器不需要资料保存的电力,不过改写资料时却要求高电压与高电流,换言之SoC内建上述存储器必需追加制程与新材料,即使量产时还是需要面临劳力、作业时间、新制程设备增加等诸多问题。

(a) 存取时间与记忆容量 (b) 消费电力与改写必要电压

图3 混载存储器的功能与用途

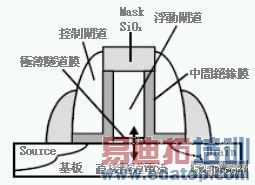

图4是新型DTM的cell结构,由图可知它与快闪存储器的结构非常类似,DTM最大特征是它的cell可以利用与一般CMOS制程相同的材料制作,因此不需使用新材料与新制程设备,而且容易与SoC进行整合,此外它可以维持原来的结构大幅缩减外形尺寸,当作大容量混载存储器使用。

结构上DTM与快闪存储器一样,利用被绝缘膜挟持的floating闸道内有无储存电子,记录0与1的数位资料,快闪存储器为维持10年以上的资料保存性,因此隧道(tunnel)膜层厚度高达10nm左右,相较之下可以高速动作的DTM膜厚却只有3nm,尤其是膜厚低于3nm的领域,量子效应会造成电子从隧道膜层逃逸,进而导致直接隧道(director tunnel)电子增加,所以DTM可以高速注入电子。

目前最先进SoC的闸道绝缘膜层厚度只有1nm左右,虽然薄闸道膜层量产上并无不妥,不过储存在floating闸道内的电子,极易通过薄的隧道膜层逃逸至基板,进而造成floating闸道几乎无法达成维持10年以上的资料保存性,因此DTM未被当成非挥发性存储器使用,它与DRAM一样通常被当成可以随伴改写(reflash)动作,作非挥发性存储器使用。

图4 DTM的cell结构

对SoC混载存储器而言,资料的读写速度非常重要。由图5可知对厚度1.6nm的隧道膜层施加5V的闸道电压时,可以获得10ns的DTM资料写入速度,随着时间的经过,储存在floating闸道内的电荷通过隧道膜层逃逸,同时还会决定电荷完全消失之前读取资料与再度在相同cell写入亦即抹写(reflash)动作的时间。

不过频繁进行抹写动作时,保持资料的消费电力相对增加,这意味着DTM元件当作替代存储器的价值大幅降低,因此研究人员透过DTM元件结构的最佳化设计,成功达成10秒的资料保持时间,若与同样进行抹写动作的DRAM比较,未来DTM可望达成2位数以上抹写间隔长期化目标。

类似影像处理在一定间隔资料全部抹写等应用,换言之若有1秒以上的资料保持时间,理论上就不需要作抹写动作,然而实际上5V的电压明显偏高,因此研究人员根据DTM元件模拟分析进行参数最佳化设计,试图藉此达成低电压目标。

根据模拟分析结果显示,隧道绝缘膜层厚度1.1nm,对高速化具有正面助益;调整基板浓度或是floating浓度,可以有效延长资料保持时间。

经过最佳化设计DTM元件在3.3V的动作电压条件下,能够获得10ns存取速度与2.5秒的资料保持时间。

图5 DTM写入的特性

FRAM强诱电存储器的技术动向

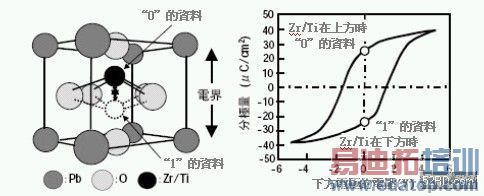

如图6所示FRAM存储器可以使强诱电体膜层的分极特性对应0与1的数字资料,即使将电压设定成0并去除外部电界,存储器仍旧可以维持它的分极特性,因此FRAM能够被当作非挥发性存储器使用。

(a) PZT的结晶构造 (b) PZT的滞延特性

图6 强诱电体结晶的基本特性

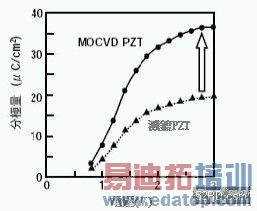

FRAM存储器最大特征是它的低消费电力特性,因此广泛应用在悠悠卡( smart card)等要求低消费电力商品。目前FRAM的量产大多使用溅镀技术制作,次世代FRAM则要求更大的记忆容量与低电压动作,为达成上述目标必需改用可以制作更密緻膜层,同时可以提高分极特性的有机金属化学气相长膜技术(MOCVD)制作(图7)。

由于CMOS世代更新电源电压相对降低,因此低电压时的分极特性大小越来越重要。如图7所示利用MOCVD可望提高低电压领域的特性,因此研究人员正积极开64Mbit的FRAM。

图7 PZT膜层的长膜方式与分极特性

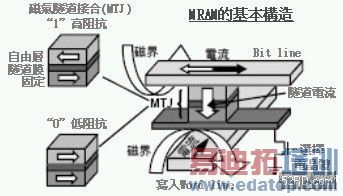

MRAM强诱电存储器的技术动向

如图8所示MRAM存储器利用磁气隧道接合(MTJ: Magnetic Tunnel Junction)的磁气阻抗值大小记录资料,基本上它是利用厚度只有1nm隧道绝缘膜层上下强磁性体薄膜的回旋(spin)平行或是反平行,使在MTJ流动的隧道电流值相异,此时若将下方强磁性体薄膜的回旋方向固定,接着改变上方自由层强磁性体薄膜的回旋方向,如此一来随着流入导线的电流就能够产生必要的磁界。

由于施加磁场时会引发回旋反转变成非挥发性存储器动作,该反转是在奈米秒以下高速产生的现象,因此理论上它能够作高速的资料改写。

此外上述反转现象不会随着材料结构改变,即使反覆反转特性也无劣化之虞,因此可当作高速大容量非挥发性存储器使用。

图8 MRAM的Cell构造

实际上MRAM存储器的开发面临下列课题,分别是:

⑴对应0与1的MTJ磁气阻抗变化率(MR比)只有50%左右,因此抑制MTJ的磁气阻抗散乱非常重要。

⑵资料写入时在导线内部流动的电流高达5mA,因此必需确保导线的可靠度。

⑶半导体制程微细化若将MTJ压缩低于100nm时,使旋转反转的必要磁界相对提高,其结果对程微细化反而变成障碍。

⑷资料写入时邻近cell非常不稳定,资料可能遭到更改,因此必需开发具备ma rgin的资料写入技术。

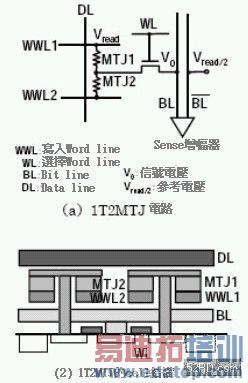

有关第⑴项课题抑制MTJ的磁气阻抗散乱影响,研究人员开发1T2MTJ回路技术(图9),它是将资料相补性写入2个MTJ,再读取一倍的阻抗差藉此确保margin。具体方法是将一个选择用电晶体连接于一个MTJ,利用一般1T1MTJ方式增加构成要素,藉此抑制MTJ的磁气阻抗散乱影响。

此外研究人员发现Al2O3隧道绝缘膜改用MgO膜,可以使50%的MR比提高4倍变成200%,改用MgO膜还能够使1T2MTJ的电路界限(margin)提高,同时作高速动作。

有关第⑵与第⑶项课题,研究人员普遍认为MTJ的材质与层的结构必需作突破性改变才能获得解决;有关第⑷项课题,透过MTJ的加工形状最佳化设计,可以有效抑制对邻近cell的影响,未来可望利用150×200nm左右的MTJ,制成64Mbit等级的混载MRAM。

图9 1T2MTJ电路方式

结语

以上介绍可以解决SoC用混载存储器SRAM课题的DTM、FRAM、MRAM最新技术动向,除此之外使用相变化材料GeSbTe的PRAM(Phase change Random Access Memory)、使用阻抗变化材料PrCaMnO与NiO的RRAM(Resistance Random Access Memory)、使用奈米碳管的存储器、使用SOI的电容DRAM则是备受期待的候补选择。

事实上至今还没有可以完全满足所有条件的存储器,因此研究人员只能充分应用各元件的特性开发次世代SoC用混载存储器,尤其是在系统内整合存储器对SoC而言,它是达高性能、低消费电力重要因素,这意味着替代存储器的开发具有重大影响。

上一篇:数字化电源的优势

下一篇:量测基础篇-DAQ基本要素与资料截取概念