- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

模拟电路设计(四)试作Head Phone

前面三篇分别介绍各种实验电路的波形。对模拟电路初学者而言,实际体验有关模拟电路的微妙变化是非常重要的一环,所以接着要利用OP增幅器的单电源与缓冲器的效果试作Head Phone,藉此体会模拟电路的奥秘。 | |||||||||||||

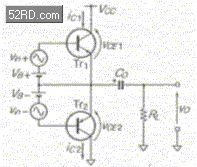

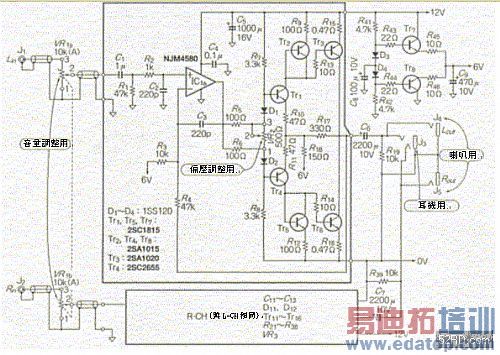

图1 与OP增幅器组合的complimentary SEPP电路

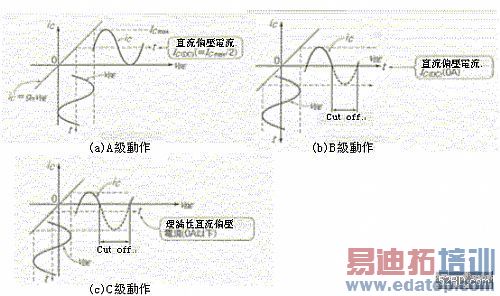

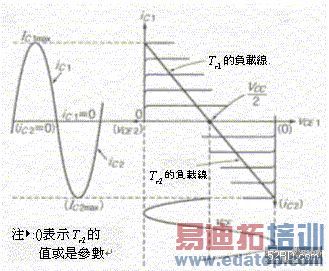

图2 增幅电路的各动作阶级与电晶体的动作特性

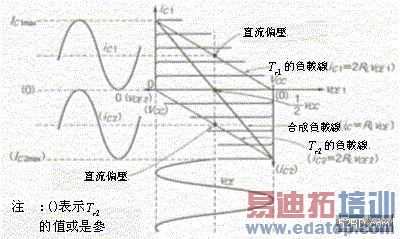

图3 A级动作的波形

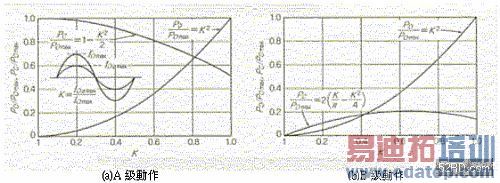

而最大效率 则可用下式求得:

图4 动作阶级与K、Pc 、Po 的关系

根据以上的计算式可知,到目前为止的B级动作特性与A级完全相同,也就是说输出电力取决于电源电压与负载阻抗,而与动作阶级无关,唯一与A级动作不同的是collector损失,它的计算式如下所示: collector损失变成最大的条件是 从电源输出的input电力PDC ,计算方法如下所示: 根据上式计算的结果得知,本电路的电力最大效率大约是78.5%,这意味着B级动作效率的改善幅度比A级动作更大。图4(b)是用 Pomax正规化后的 K与 Pc 、Po 三者的互动关系图。  图5 B级动作的波形

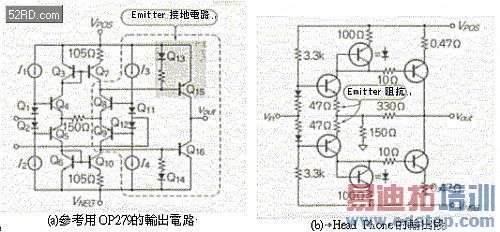

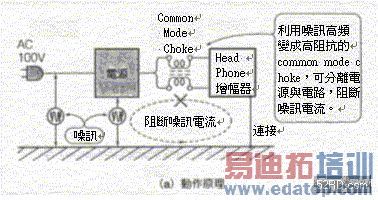

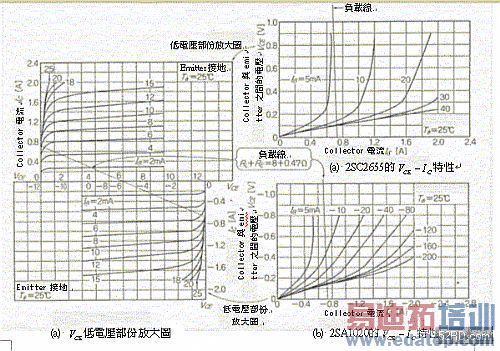

AB级的歪斜与损失较少 图4(a)与图4(b)两者相互比对时,可发现B级的损失比较少,不过图6的电晶体VBE-Ic 传达特性,在低电压时会出现非直线性变化,进而造成VBE之间因二极管特性产生cross over斜歪,所以必需依照图6(b)所示,流入微量偏压电流藉此消除cross over歪斜,上述微量偏压电流称为idling电流,由于它是在A级与B极之间流入偏压电流,所以又称为AB级。通常AB级的偏压电流非常微弱少量,它的效率几乎与B级相同,而且是属于歪斜很小的动作,因于此本文的试作电路全部使用AB级动作。  图6 AB级push-pull电路与cross over偏斜的关系 输入段的设计 採用rail to rail输出使振幅动作 在类比电路讲座第二篇曾经介绍实验用的complementary emitter follower。负载为100Ω时,它的输出会在 VCC-5V~VEE+5V之间振幅,因此12V单电源只能获得2Vp-p 左右的输出。此外基于rail to rail OP增幅电路的设计理念,所以将电路设计成如图7(a)所示的emitter接地输出段,因为只要emitter接地,就算饱和电压很低,由于偏压(bias)电流已经稳定化,所以即使输入emitter阻抗,输出振幅仍然能够取得充分的10Vp-p ,因此图7(b)的输出电路也採用上述的设计方式。根据实验结果显示8Ω的负载,可以获得11Vp-p 左右的输出振幅,图7(c)是它的实际电路。由于它与Gain 3.2倍非反转增幅器成等价状态,所以前段OP增幅器必需具备11/3.2=3.5 Vp-p的电压,必需注意的是如果过度扩张Gain值会引发各种问题,所以此处的Gain值暂定为3.2。与base连接的二极管或是与二极管连接的电晶体,则被设计成可以补偿 VBE同时还可稳定偏压电流。虽然monolithic IC即使无emitter阻抗亦能稳定动作,不过类似这种使用disc lead transistor的场合,就需设置emitter阻抗。   散热设计 设计功率增幅器(power amplifier)首要工作是处理散热问题。如众所知通常只要决定输出段的结构就可求出耗电量。此处假设负载为8Ω,K=1 ,接着将它代入式(11)就可求出每个频道(channel)的耗电量: 由于stereo具有两个频道,所以电源电流IDC 的计算如下: 各频道的偏压电流大约是20mA左右,所以用0.52A作概括计算,如此一来输出段电晶体的最大损失,根据式(10)的计算大约是0.46W。 如上所述本电路具有偏压电流,所以上述最大损失基于裕度考量以0.6W概括计算。此外假设增幅器内部最大温度500C , 2SA1020与2SC2655两电晶体根据规格(3)、(4)的规定,无heat sink时的最大工作温度为650C ,由于该电晶体需与温度补偿电晶体作热结合,因此两者以近贴方式封装,之后再用silicon粘着剂作热结合。值得一提的是若未作温度补偿,电路不但会出现温升,同时偏压电流还会大幅升高,电晶体的损失增加,最后导致电子元件受到破坏,虽然加大emitter阻抗可以防止发生上述问题,不过如此一来却会使损失增加输出电力降低,所以必需使功率增幅器的emitter阻抗,维持在最小范围进行温度补偿,详细内容请参考类比电路讲座第一篇「有关电晶体电路设计」的说明。 ‧电源电路的设计 1.使用AC变压器与三端子regulator进行电源稳定化 根据以上计算结果可知,本电路必需使用电流容量为0.52A的电源电路,此处基于成本考量,因此使用+15VCD/0.8A switching AC变压器当作电源电路。一般switching方式的电源噪讯值都非常高,如果switching方式的电源应用在类比电路就需作噪音对策,所以本店路在输出端设置noise filter与+12VDC ,藉此稳定电源电路。由图8可知经过稳定化电源电路,使用可输出12V/1A的NJM7812 IC,这种IC又称为三端子regulator;图9则是三端子regulator内部的等价电路,基本上它是用非反转增幅器,将基准电压增幅成12V,由于输出电流高达1A,所以NPN的buffer transistor设有output,此外为防止输出short造成元件损毁,因此内部还设有过热与过电流保护装置。目前switching方式的电源几乎都是使用三端子regulator,除此之外也三端子regulator也可以应用在OP增幅器。三端子regulator的损失PD ,计算方法如下所示: 根本经验显示TO-220的封装方式,无散热片(heat sink)时的电力损失最多只有1W左右,因此上述IC只设置U形散热片帮助散热。 2.利用common mode choke抑制switching noise 根据以往的经验显示,switching电源即使在output设置三端子regulator,也无法降低spike状的switching噪讯(noise),即使追加设置choke coil与condenser的noise filter,也无法有效抑制switching噪音,主要原因是switching电源的噪讯并非出现在output的+/-极之间,而是出现在大地与output lead之间,这种形式的噪音称为common mode noise。抑制common mode noise最佳方式是使用common mode filter。如图10(b)所示所谓的common mode choke coil是由两条卷线所构成,它与一般的线圈(coil)最大差异是output端几乎无电感(inductance)存在。图11是filter的电感实测结果,由图可知common mode inductance 为5mH,normal mode inductance 则为72μH,流入大地与output lead直列的inductance变成5mH,也就是说common mode filter就是利用该5 mH的电感阻断common mode noise 。  图10 common mode choke coil的基本结构与功能

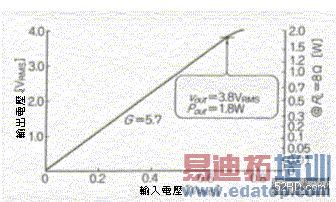

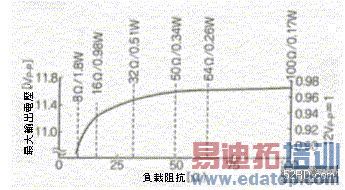

照片1(a)是switching AC变压器output的噪音波形;照片1(b)是三端子regulator的输出波形,由照片可以看出它的输出波形已经缩小成1/10,尤其是尖锐脉冲状的spike noise几乎完全消失。如上所述虽然三端子regulator能抑制导线之间的ripple noise,不过仍然会输出spike noise,因此利用common mode choke减缓spike noise,因为模拟电路使用switching type电源时,利用common mode choke通常都可以有效抑制spike noise。  照片1 电源电路的输出ripple noise的波形(0.5mV/div,2μs/div) 3.增幅器的设计 OP增幅器使用audio用NJM4580 IC,图12是NJM4580 IC与图7(a)的emitter接地complimentary buffer,两者组合成构成非反转增幅器,它的Gain为5.7倍,如果Gain不足时可以变更R4(R24) 改变设定值,此外output设有音量调整用volume,有关电容器的容量决定方法,将在本模拟电路讲座第4篇作详细说明,此处则以图中的标示值为基准。喇叭用jack左右共计两个。决定动作点的 6V(=VCC/2)内部电源,是用Tr7 与Tr8 的complimentary emitter follower产生。除此之外本电路还具有减少电容器的数量与容量两种功能。为评估输出电力因此在电晶体的IC-VCE 特性中,追加设置RE=0.47Ω 的emitter电阻,并描绘如图13所示的负载线,依此假设 的最大值为0.85(8Ω负载时)与0.9(32Ω负载时),再根据式(3)分别计算 P0值,计算结果如下所示:

根据以上的计算得知本电路完全符合100mW的设计规格,至于其它内部损失造成的输出减损,则根据实验结果作判定。  图12 Head Phone增幅器电路设计图

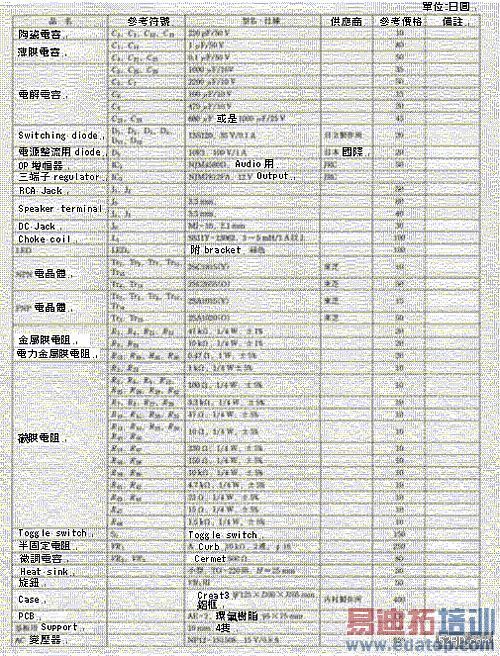

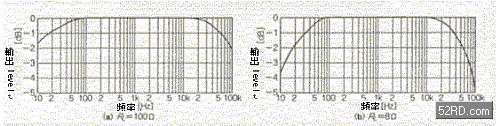

图13 Head Phone增幅器输出段的电晶体动作特性 3.如何制作Head Phone 表1是Head Phone增幅器电路的元件一览表。图8电源单元使用两个680μF电解电容,主要原因是为了抑制内部元件高度,以便符合20~25mm的设计规格。最终段电晶体与温度补偿用电晶体,则是用silicon粘着剂作热结合。图8增幅单元的12V电源与零V接地,分别与C25 与C26 连接;音量调整用volume与偏压电流调整用volume的配线,被layout成顺时针方向旋转时为增量,逆时针方向旋转时为减量。组装完成后为了确认配线的正确性,所以将 VR2与VR3 朝逆时针方向旋转使电路导通,并将相同信号input至左右两个输入端,藉此检查输出是否正确。电路导通30分后再将 朝逆时针方向全开,使 R16与R36 两端的电压变成10mV左右,接着再朝顺时针方向旋转 VR2与VR3 ,使偏压电流变成20mV左右。虽然最终段电晶体与温度补偿用电晶体,使用silicon粘着剂作简易的热结合,不过使用前偏压电流会逐渐增加,使用后不可以有任何变动才算正常。  表1 Head Phone的元件一览表 4.实测特性 ‧频率特性/Gain/输出电力的确认 图14是Head Phone的频率特性,由图可知Head Phone的频率特性在8Ω负载时,-3dB频率范围为12Hz~77kHz,若从图15的输出入特性计算Gain时,可获得5.6几乎与设计值一致的结果;最大输出电力若依照图16的特性计算,其结果几乎与设计值完全相同,由此可知内部损失并未造成输出降低  图14 Head Phone增幅器的输出频率特性

图15 Head Phone增幅器无信号时的output noise

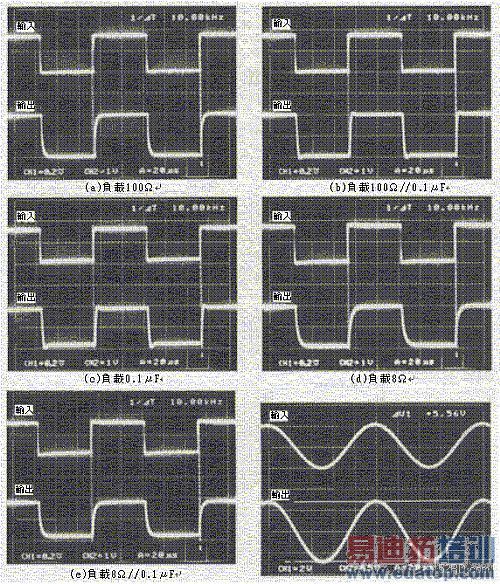

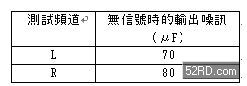

图16 Head Phone增幅器的负载阻抗与最大输出电压 ‧确认发振特性 为了确认audio增幅器的稳定性,所以在输出端设置电容器,藉此观察方形波形信号输入时的波形。首先确认电路未作发振,接着再确认是否产生over shoot与ringing。照片2是输入10kHz方形波时的输出波形,依此波形可知阻抗负载时的波形相当漂亮,即使并连0.1μF的负载阻抗,它的波形也非常令人满意,若拆掉电阻改成0.1μF的电容,其结果与100Ω设置0.1μF电容几乎完全相同,这意味着本增幅器不易发振而且非常稳定,尤其是8Ω负载时不论有无电容器,它的波形完全未变化,显示本增幅的动作非常稳定。 ‧歪斜特性与输出噪音 由于本讲座第4篇将介绍stram gage,因此有关歪斜特性留在第4篇说明。照片是10kHz正弦波的输入波形,从照片中几乎未看到任何歪斜,依此推论歪斜应该低于1%以下,表2是输入噪音特性,由表可知本电路的输出噪音大约是70μV~80μV左右。  照片2 10kHz方形波的输出波形特性 照片3 10kHz正弦波的输出波形特性  表2 Head Phone增幅器无信号时的输出噪音 ‧消费电力 如表2所示本Head Phone增幅器最大输入电力为7.8W,远低于AC变压器(adapter)12W的最大输出,显示本电路具有宽广的动作裕度。对小型电子机器而言,输出电力与内部损失两者的总合就变成输入电力,换句话说只要在input端控制输入电力,就能有效抑制输出电力与内部损失。  |

上一篇:2.75W低成本USB充电器/适配器参考设计

下一篇:什么是过冲(overshoot)和下冲(undershoot)