- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何降低MIPS CPU 50%的动态功耗

设计CPU需要很多技巧和努力。拿到一个CPU设计并降低其50%的动态功耗需要一系列特殊的技巧,这也是CPU设计人员漫长职业生涯的要取得的技能之一。

在成功推出第一款PowerVR Rouge GPU的DOK后,Imagination和Synopsys展开第二个项目合作,旨在不牺牲任何性能领先数字的前提下显著降低MIPS处理器的功耗。

动态功耗是SoC设计人员中一个热门的(请原谅这个双关语)话题

降低动态功耗是很多系统芯片设计人员目前面临的一大挑战。对可综合IP来说目前有各种不同的选择和考虑因素。同一IP可以应用在不同市场中的各式各样应用中。最重要的是,工艺、工具和流程是额外需要考虑的挑战。

性能、功耗和面积(PPA)的权衡取舍不同,依赖于不同的工艺,也依赖于客户的实现要求。

Synopsys公司最近组织的一期研讨会一文总结了来自于Imagination公司的Maya Mohan和NageshSakhamuru提出的一些选项,可用于Synopsys工具与流程使用28nm技术的情景下。

其主要目标是使用特定的工艺和各子库方案与Synopsys工具和流程结合的时候,介绍给SoC设计人员能够节省动态功耗的各个方面。作者把很多重点放动态功耗相对于泄漏功耗上,并给出了特定技术库IP选择时每一步骤和流程阶段相应的功耗降低情况。

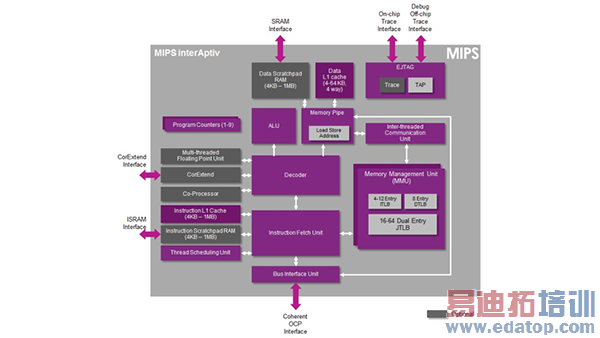

这个项目中CPU选择的是MIPS interAptiv,它属于Aptiv家族,是一个超高效的多线程处理器。在一般情况下,CPU期望以最高性能运行,同时保持动态功耗尽可能地低。然而,以峰值性能运行也可能会增加动态功耗;这就引发了需要寻找方法在持续性能与降低功耗之间取得平衡。

动态功耗有多个部件

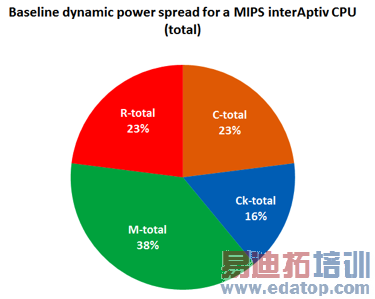

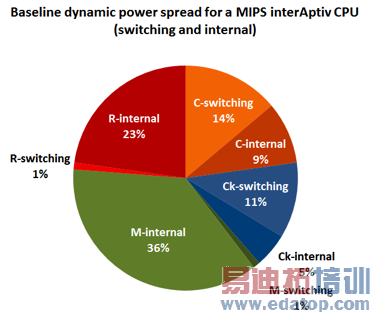

您可以在一个CPU核心找到各种动态功耗部件,标记如下:存储器(M-Power),指令和数据高速缓存,寄存器(R-power),叶级的时钟门控和非门控的寄存器,时钟网络单元(Ck-power),时钟门控和缓冲区以及组合单元(C-power)。

对于每个以上四个分类,又细分为两个子部件:内部功耗和开关功耗。每一部分都被单独分析,并且在每次动态功耗优化时各种选项也都会被考虑。

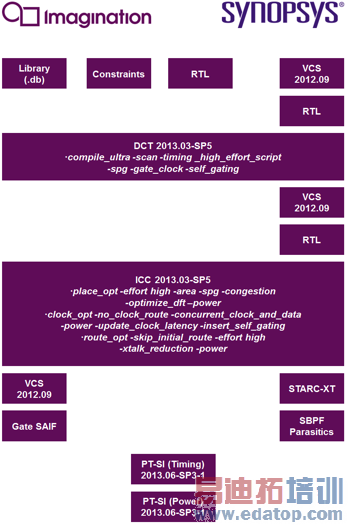

综合在DCT/ DCG中进行,而布局布线则在ICC中执行。两个阶段都测量了功耗:DCT后期以及ICC后期。基于一致性考虑,研讨会所有报告的功耗数据都取自ICC后期数据库,通过门级仿真的开关行为获得。参数提取由StarRC完成,Dhrystone诊断在门仿真时被使用,PT-PX用于功耗测量。

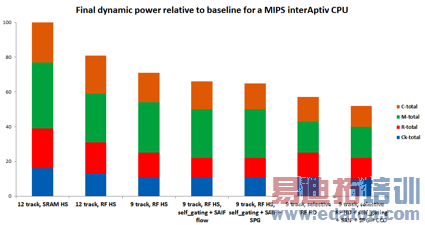

上图显示了MIPS interAptiv CPU的总动态功耗的各个子部件。这个基线版本被用于其它方法和实验进行比较的对象。

通常动态功耗使用mW/ MHz测量,但对于本项目,基线版本运行的总功耗被归一化为100,其它版本的运行功耗基于这一数字得出。

正如从上图中所看到的,时钟功耗只点总功耗的约16%。从这里的图表中,我们不难看出,功耗的最大消费者是内部存储器和寄存器,以及组合逻辑的开关功耗:

•开关功耗正比于开关电容大小和切换次数。为了提高寄存器和组合逻辑的功耗水平,在DCT中大部分优化使用了基于RTL的SAIF与自我门控技术。在ICC中各种动态功耗降低特性也在网络研讨会中进行了探讨,以及运行最后阶段的新CCD(并行时钟和数据)特性。

•内部功耗正比于单元的数目、单元大小和切换次数。降低寄存器的内部功耗可通过替换为较小尺寸的单元以及降低切换次数。也可以使用更低轨道的工艺库(例如,从12轨道转换至9轨道)提供了相对于性能和面积降低功耗的另一种折衷。内部存储器的功耗主要归因于所选择的大小或存储器类型。Synopsys的存储器编译器有多种内存可供选择。笔者选择了一个基于RF的组合,结合了高性能以及高密度的单端口存储器,这种组合一般用于平衡(高效的)功耗/性能需求。

非常令人激动的结果!

所有上述特性和技术的结合在一起显著降低了功耗。下面的流程图描述了Synopsys的综合工具和ICC中所使用的最终工具选项:

在项目结束时,总功耗降低了约48%,面积减少了46%,而代价为只降低了CPU15%的性能表现。

上表显示了所有上述实验和相应功耗;要查看完整结果,请下载完全白皮书,下载后您会看到这个过程中每一步骤对应功耗和面积的减少。