- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

实用EMI噪声对策讲座(14) 数字电路

早期CMOS的动作速度非常迟缓,目前B家族系列的CMOS广泛应用在各种领域,随着IC设计、制作技术的进化,高速化的CMOS动作速度几乎凌驾LSTTL。CMOS问世后曾经是数字IC的主流,目前已经被兼具CMOS低消费电力与TTL高速特性的BiCMOS系列取代。

数位IC的类别

数字IC的家族成员可以分成:

*TTL

*CMOS

*其它

等三大类。CMOS是互补(complementary)MOS的简写,它是二个MOS型晶体管成对(pair)状结构;TTL则是由双极(bipolar)晶体管构成,全球首颗IC就是TTL type,因此TTL又称为标准TTL。标准TTL问世不久陆续出现其它TTL家族成员,目前标准TTL几乎完全退出市场。

演算理论

数字IC是执行理论演算的主要组件之一,虽然大规模电路不断被IC化制成所谓的「ASIC」,不过基本上任何一种IC都是理论演算集合的结果。

理论分成二值理论与多值理论两种型式,实际上大多采用二值理论方式,二值理论具有两种状态,该二值称为「真」与「伪」,分别使用:

*1→真

*0→伪

二进制的数值。虽然数位IC再将1定义成高(H: High)电压,0定义成低(L: Low)电压,但不论是”H”或是”L”电压两者都是对等。「1为高电压,0为低电压时称为正理论」;「1为低电压,0为高电压称为负理论」。理论演算大致上可以分成:

*组合理论

*顺序理论

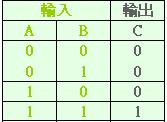

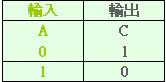

两种。所谓组合理论是指输出与输入会比照1对1,一旦决定输入的理论值,对应的输出就会自动决定。表1~表3分别表示理论的真理论值,它也是组合理论的基本要素。

表1 AND的真理论值

表2 OR的真理论值

表3 NOT的真理论值

如上所述,可以实现基本组合理论的IC称为网关(gate)IC。所谓顺序理论是指过去的状态影响目前的输出,目前的输出却不能决定目前的输入,亦即它是指记忆过去状态的功能而言。

双稳态电路(FF:Flip Flop)就是典型可以实现顺序理论的IC,双稳态的基本型是RS-FF IC,虽然RS-FF IC能够以输入强度(level)动作,不过目前常用的IC大多采用输入端缘(edge)动作,因此又称为端缘触发双稳态电路(ETFF:Edge Trigger Flip Flop),其中又以D-FF IC最具代表。

TTL与CMOS的比较

CMOS广泛应用在各种电子电路,因此TTL与CMOS比较时,会涉及许多噪讯对策的动作机制,一般而言CMOS的抗噪讯能力确实比TTL强大,不过它的公认强大抗噪讯原因却不代表完全正确,而且CMOS本身在噪讯对策上有许多问题点与盲点,因此使用上必需格外谨慎。

所有的数字IC都有噪讯界限(noise margin)限制,反过来说由于有噪讯界限的限制,因此数字IC的抗噪讯能力非常强大,在一般噪讯环境下通常都可以安全使用。

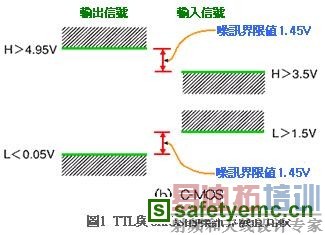

CMOS的噪讯界限与电源电压呈比例,电源电压与标准TTL的电源电压相同,图1是5V时CMOS与TTL数字IC的比较结果。

由图可知,TTL的噪讯界限值为0.4V,CMOS为1.45V,因此C-MOS的噪讯界限值比TTL强,不过抗噪讯强度并不是单纯取决于电压,除了电压之外例如阻抗(impedance)等等也是原因之一,此外是驱动器的输出阻抗,对印刷电路基板的布线阻抗具有支配性影响。

TTL与CMOS若分别使用LS与HC家族系列数字IC,HC的驱动阻抗非常高会抵销噪讯界限值的大小,其结果造成几乎没有明显的抗噪讯强度差异。

相较之下,TTL与CMOS,若采用LS与AC家族系列数字IC,由于AC家族系列数字IC的输出阻抗非常低,因此它的抗噪讯特性反而比TTL更优秀。

EMC电磁兼容设计培训套装,视频教程,让您系统学习EMC知识...

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

上一篇:实用EMI噪声对策讲座(18)

比较器

下一篇:EMI滤波器的技术与设计