- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高电源抑制比性能的线性稳压器

录入:edatop.com 点击:

方法1──增加一个线性稳压器。这种方法非常简单,仅需占用少量PCB面积(如AS1358-9要用到2个TSOT23-5封装),与其它方法相较设计时间最短。将两个线性稳压器串联,可使任何频率点的PSRR增加一倍(假设两个稳压器完全相同)。这种方法的缺点是压降会加倍,而且需一个额外的电容。两个AS1359串联后的典型压降在300mA负载电流时为280mV,在100kHz时的抑制比为120dB。要达到这样的水平,必须仔细处理组件的布局和PCB走线。

从实用角度考虑,每个LDO上应允许350mV到400mV的压降。AS1358-9 LDO稳压器的输出电压范围为1.5V到4.5V,调整步进是50mV,因此特殊电压不是问题。

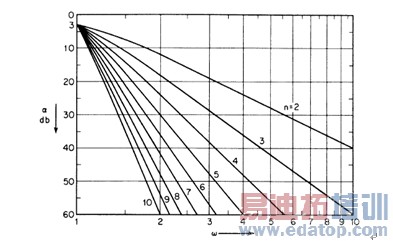

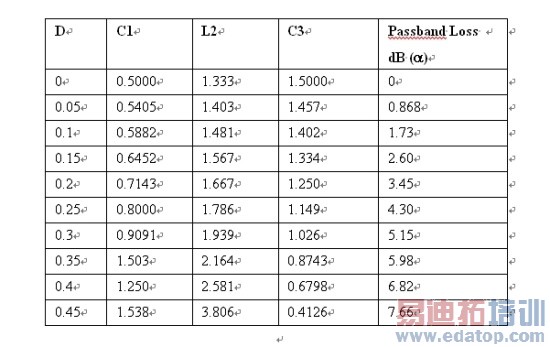

方法2──输入端加载基于统一耗散网络的LC滤波器。三极点巴特沃斯特性需要串联低值线圈和两个电容,其中一个电容通常位于LDO输入端。三极点巴特沃斯响应在4.5Fo处可提供额外40dB的抑制,其中Fo是-3dB点(见图5)。

图5:不同阶数N下的巴特沃斯阻带衰减。

相较方法1,额外的滤波器网络不会增加显著的直流阻抗损耗。不过设计时要特别小心,确保所选电感能够支持要求的直流电流而不至于饱和。巴特沃斯是很有用的特性,其中的通带特别平坦,这点与切比雪夫特性不同,后者为了获得更好的衰减率会牺牲通带和阻带纹波。图7显示级数在2和10之间的巴特沃斯滤波器衰减特性。

作者:Andy Fewster 来源:电子工程专辑

上一篇:一个IP分布式小型呼叫中心实例

下一篇:紧急广播技术全面解析